# Device Reference Manual Device Reference Manual

## 2 Copyright

#### **Copyright Notice**

Copyright © WestDev Ltd. 2001-2017, and SiMetrix Technologies Ltd Pulsonix is a Trademark of WestDev Ltd. All rights reserved. E&OE

Copyright in the whole and every part of this software and manual belongs to WestDev Ltd. and SiMetrix Technologies Ltd. and may not be used, sold, transferred, copied or reproduced in whole or in part in any manner or in any media to any person, without the prior written consent of WestDev Ltd. If you use this manual you do so at your own risk and on the understanding that neither WestDev Ltd. nor associated companies shall be liable for any loss or damage of any kind.

WestDev Ltd. does not warrant that the software package will function properly in every hardware software environment.

Although WestDev Ltd. has tested the software and reviewed the documentation, WestDev Ltd. makes no warranty or representation, either express or implied, with respect to this software or documentation, their quality, performance, merchantability, or fitness for a particular purpose. This software and documentation are licensed 'as is', and you the licensee, by making use thereof, are assuming the entire risk as to their quality and performance.

In no event will WestDev Ltd. be liable for direct, indirect, special, incidental, or consequential damage arising out of the use or inability to use the software or documentation, even if advised of the possibility of such damages.

WestDev Ltd. reserves the right to alter, modify, correct and upgrade our software programs and publications without notice and without incurring liability.

Microsoft, Windows, Windows NT and Intellimouse are either registered trademarks or trademarks of Microsoft Corporation.

All other trademarks are acknowledged to their respective owners.

Pulsonix, a division of WestDev Ltd.

Printed in the UK. Issue date: 12/01/17 iss 3

#### Pulsonix

20 Miller Court Severn Drive Tewkesbury Business Park Tewkesbury Glos, GL20 8DN United Kingdom

| Phone   | +44 (0)1684 296 551  |

|---------|----------------------|

| Fax     | +44 (0)1684 296 515  |

| Email   | info@pulsonix.com    |

| Support | support@pulsonix.com |

## 4 Copyright

## Contents

| CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| CHAPTER 1. SIMULATOR DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                                                                                 |

| Netlist Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                   |

| File Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                   |

| Language Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                   |

| Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |

| Device Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |

| Simulator Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

| Simulator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                   |

| The List File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

| The Binary Data File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                   |

| Output Data Names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                   |

| CHAPTER 2. SIMULATOR DEVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |

| Using XSPICE Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                   |

| Vector Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

| Connection Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                   |

| Using Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                   |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |

| Using Expressions for Device Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |

| Using Expressions for Model Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                   |

| Expression Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                   |

| Optimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |

| Opuninsauon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                   |

| *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                   |

| CHAPTER 3. ANALOG DEVICE REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29                                                                                |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>29</b><br>29                                                                   |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>29</b><br>29<br>                                                               |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>29</b><br>29<br>29<br>33                                                       |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>29</b><br>29<br>33<br>37                                                       |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor<br>Capacitor with Voltage Initial Condition                                                                                                                                                                                                                                                                                                                                                                                                            | <b>29</b><br>29<br>33<br>37<br>38                                                 |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor<br>Capacitor with Voltage Initial Condition<br>Current Controlled Current Source                                                                                                                                                                                                                                                                                                                                                                       | <b>29</b><br>29<br>33<br>37<br>38<br>39                                           |

| CHAPTER 3. ANALOG DEVICE REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>29</b> 29 29 33 37 38 39 41                                                    |

| CHAPTER 3. ANALOG DEVICE REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>29</b> 29 29 33 37 38 39 41 42                                                 |

| CHAPTER 3. ANALOG DEVICE REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>29</b> 29 29 33 37 38 39 41 42 42 42                                           |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor<br>Capacitor with Voltage Initial Condition<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3.                                                                                                                                                                                                                                                                                 | <b>29</b> 29 29 33 37 38 39 41 42 42 42 45                                        |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor<br>Capacitor with Voltage Initial Condition<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3<br>Diode – Soft Recovery                                                                                                                                                                                                                                                         | <b>29</b> 29 29 33 37 38 39 41 42 42 42 42 45 47                                  |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor<br>Capacitor with Voltage Initial Condition<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3.<br>Diode – Soft Recovery<br>GaAsFET<br>Inductor (Ideal)                                                                                                                                                                                                                         | <b>29</b> 29 29 33 37 38 39 41 42 42 42 42 42 45 45 47 48                         |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor.<br>Capacitor with Voltage Initial Condition.<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3.<br>Diode – Soft Recovery<br>GaAsFET                                                                                                                                                                                                                                           | <b>29</b> 29 29 33 37 38 39 41 42 42 42 42 45 45 47 48 49                         |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor<br>Capacitor with Voltage Initial Condition<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3<br>Diode – Soft Recovery<br>GaAsFET<br>Inductor (Ideal)<br>Inductor (Saturable)                                                                                                                                                                                                  | <b>29</b> 29 29 33 37 38 39 41 42 42 42 45 45 47 48 49 51                         |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor.<br>Capacitor with Voltage Initial Condition.<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3.<br>Diode – Soft Recovery.<br>GaAsFET<br>Inductor (Ideal).<br>Inductor (Saturable).<br>Inductor with Current Initial Condition                                                                                                                                                 | <b>29</b> 29 29 33 37 38 39 41 42 42 42 45 45 45 51 52                            |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor.<br>Capacitor with Voltage Initial Condition.<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3.<br>Diode – Soft Recovery<br>GaAsFET<br>Inductor (Ideal).<br>Inductor (Saturable).<br>Inductor with Current Initial Condition<br>Insulated Gate Bipolar Transistor<br>Junction FET<br>Lossy Transmission line                                                                  | <b>29</b> 29 29 33 37 38 39 41 42 42 42 45 45 47 48 49 51 52 53 55                |

| CHAPTER 3. ANALOG DEVICE REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>29</b> 29 29 33 37 38 39 41 42 42 42 45 45 47 48 49 51 52 53 55                |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor.<br>Capacitor with Voltage Initial Condition.<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3.<br>Diode – Soft Recovery.<br>GaAsFET<br>Inductor (Ideal).<br>Inductor (Saturable).<br>Inductor with Current Initial Condition<br>Insulated Gate Bipolar Transistor<br>Junction FET.<br>Lossy Transmission line<br>MOSFET.<br>Resistor                                         | <b>29</b> 29 29 33 37 38 39 41 42 42 42 42 45 45 47 48 49 51 52 53 55 56 62       |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source.<br>Bipolar junction transistor<br>Capacitor.<br>Capacitor with Voltage Initial Condition.<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source.<br>Diode – Level 1 and Lvel 3.<br>Diode – Soft Recovery.<br>GaAsFET<br>Inductor (Ideal).<br>Inductor (Saturable).<br>Inductor with Current Initial Condition<br>Insulated Gate Bipolar Transistor<br>Junction FET.<br>Lossy Transmission line<br>MOSFET.<br>Resistor.<br>S-domain Transfer Function Block. | <b>29</b> 29 29 33 37 38 39 41 41 42 42 42 45 45 47 48 49 51 52 53 55 56 62 62 64 |

| CHAPTER 3. ANALOG DEVICE REFERENCE<br>Overview<br>Arbitrary Source<br>Bipolar junction transistor<br>Capacitor.<br>Capacitor with Voltage Initial Condition.<br>Current Controlled Current Source<br>Current Controlled Voltage Source<br>Current Source<br>Diode – Level 1 and Lvel 3.<br>Diode – Soft Recovery.<br>GaAsFET<br>Inductor (Ideal).<br>Inductor (Saturable).<br>Inductor with Current Initial Condition<br>Insulated Gate Bipolar Transistor<br>Junction FET.<br>Lossy Transmission line<br>MOSFET.<br>Resistor                                         | <b>29</b> 29 29 33 37 38 39 41 41 42 42 42 45 45 51 52 53 55 56 62 62 64 69       |

| Voltage Controlled Current Source                     |    |

|-------------------------------------------------------|----|

| Voltage Controlled Switch                             |    |

| Voltage controlled voltage source                     |    |

| Voltage Source                                        |    |

| Pulse Source                                          |    |

| Piece-Wise Linear Source                              |    |

| PWL File Source                                       |    |

| Sinusoidal Source                                     |    |

| Exponential Source                                    |    |

| Single Frequency FM                                   |    |

| Noise Source                                          |    |

| Extended PWL Source                                   |    |

| Mutual Inductor                                       |    |

| CHAPTER 4. DIGITAL SIMULATION                         | 83 |

| Logic States                                          |    |

| State resolution table                                |    |

| Analog to Digital Interfaces                          |    |

| How A-D Bridges are Selected                          |    |

| Logic Families                                        |    |

| Logic Family Model Parameters                         |    |

| Logic Compatibility Tables                            |    |

| Supported Logic Families                              |    |

| Universal Logic Family                                |    |

| Internal Tables                                       |    |

| Load Delay                                            |    |

| Digital Model Libraries                               |    |

| Using Third Party Libraries                           |    |

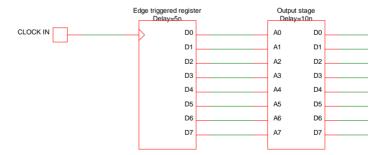

| Arbitrary Logic Block - User Defined Models           |    |

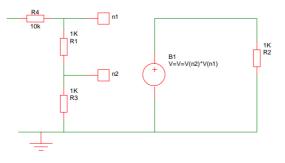

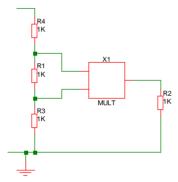

| Example 2 - A Simple Multiplier                       |    |

| Example 3 - A ROM Lookup Table                        |    |

| Example 4 - D Type Flip Flop                          |    |

| Device Definition - Netlist Entry & .MODEL Parameters |    |

| Language Definition - Overview                        |    |

| Language Definition - Constants and Names             |    |

| Language Definition - Ports                           |    |

| Language Definition - Registers and Variables         |    |

| Language Definition - Assignments                     |    |

| Language Definition - User and Device Values          |    |

| Diagnostics : Trace File                              |    |

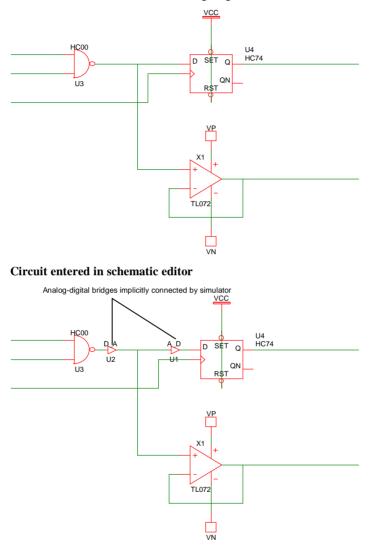

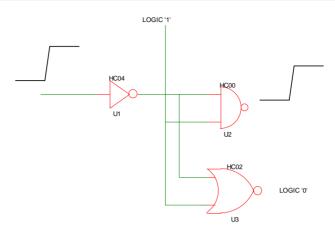

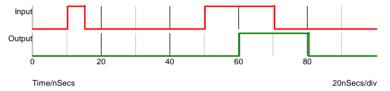

| Mixed-mode Simulator - How it Works                   |    |

| Event Driven Digital Simulator                        |    |

| Interfacing to the Analog Simulator                   |    |

| Enhancements over XSPICE                              |    |

|                                                       |    |

| CHAPTER 5. DIGITAL DEVICE REFERENCE                   |    |

| Digital Device Reference                              |    |

| Common Parameters                                     |    |

| Delays                                                |    |

| And Gate                                              |    |

| D-type latch                                          |    |

| D-type flip flop                                      |    |

|       | Buffer                          | 115 |

|-------|---------------------------------|-----|

|       | Digital Capacitor               | 117 |

|       | Frequency Divider               | 120 |

|       | Digital Initial Condition       | 121 |

|       | Digital Pulse                   | 122 |

|       | Digital Resistor                | 123 |

|       | Digital Signal Source           | 124 |

|       | Inverter                        | 127 |

|       | JK Flip Flop                    | 128 |

|       | Arbitrary Logic Block           |     |

|       | Nand Gate                       | 132 |

|       | Nor Gate                        | 133 |

|       | Open-Collector Buffer           | 134 |

|       | Open-Emitter Buffer             | 135 |

|       | Or Gate                         | 137 |

|       | Pulldown Resistor               | 138 |

|       | Pullup Resistor                 | 138 |

|       | Random Access Memory            | 139 |

|       | Set-Reset Flip-Flop             | 140 |

|       | SR Latch                        | 142 |

|       | State Machine                   | 144 |

|       | Toggle Flip Flop                | 145 |

|       | Tri-State Buffer                | 147 |

|       | Exclusive NOR Gate              | 148 |

|       | Exclusive OR Gate               | 149 |

|       | Analog-Digital Converter        | 150 |

|       | Analog-Digital Interface Bridge | 153 |

|       | Digital-Analog Converter        | 157 |

|       | Digital-Analog Interface Bridge | 159 |

|       | Controlled Digital Oscillator   |     |

|       | Analog-Digital Schmitt Trigger  | 163 |

| INDEX |                                 | 66  |

|       |                                 |     |

## 8 Contents

## **Chapter 1. Simulator Data Formats**

## **Netlist Format**

The Pulsonix Spice netlist format follows the general format used for all SPICE and SPICE compatible simulators. However, with so many SPICE derivatives and with two significantly different versions of SPICE itself (SPICE 2 and SPICE 3) it is not possible to define a standard SPICE format. Pulsonix Spice has been developed to be as compatible as possible with model libraries that can be obtained from external sources.

For discrete devices, models are usually SPICE 2 compatible but some use extensions originally developed for PSpice<sup>®</sup>. IC designers usually receive model files from fabrication companies and these tend to be developed for Star-Hspice<sup>®</sup>. Pulsonix Spice is compatible with all of these but simultaneous compatibility with all formats is not technically possible due to a small number of syntax details - such as the character used for in line comments. To overcome these minor difficulties, a language declaration can be placed at the top of the netlist and any file included using .INC or the Star-Hspice<sup>®</sup> variant of .LIB. This is described in the following sections.

## File Format

A complete netlist consists of:

- A title line

- Optional language declaration

- Device lines

- Control lines

- Comment lines

The title line must be the first line of the file and may be empty. The remaining lines, with some exceptions, may be placed in any order

All other lines are defined by their first non-whitespace character as follows.

- Control lines begin with a period: '.'

- Comment lines begin with an asterix: '\*'

- Device lines begin with a letter

A line is usually terminated with a new line character but may be continued using the '+' continuation character. So if the first non-whitespace character is a '+' the line will be considered to be an extension of the previous line. SPICE requires the '+' to be the first character, Pulsonix Spice allows whitespace (space or tab) to precede it.

#### Language Declaration

Pulsonix Spice is able to read PSpice<sup>©</sup>, Star-Hspice<sup>©</sup> and native Pulsonix Spice netlists, but in some cases needs to be instructed what format netlist it is reading. Currently there are three areas where simultaneous compatibility has not been possible. These are:

- Inline comment character.

- Unlabelled device parameters

- The meaning of LOG() and PWR() functions

Pulsonix Spice can be instructed to use any of the two non-native languages by using the language declaration. This is one of:

\*#HSPICE \*#PSPICE

The language declaration must be placed at the top of the file immediately below the title line. It can also be placed in files referenced using .INC or the HSPICE© version of .LIB in which case it will apply only to that file and any others that it calls. A language declaration placed anywhere else in a file will be ignored.

## Comments

Any line other than a language declaration beginning with a '\*' is defined as a comment and will be ignored. Also anything between a semi-colon ';' (\$' in HSPICE mode) and the end of the line will be treated as comment and will also be ignored. Some SPICE simulators require the '\*' character to be the first character of the line. Pulsonix Spice allows it to be preceded by white space (spaces and tabs).

## **Device Lines**

Device lines usually follow the following basic form but each type of device tends to have its own nuances:

Name nodelist value [parameters]

*value* may be an actual number e.g. in the case of passive components such as resistors, or it may be a model name in the case of semiconductor devices such as bipolar transistors. Models are defined using a .MODEL control line.

*nodelist* is a list of net names. The number and order of these is device dependent. The net name itself may consist of any collection of non-control ASCII characters except whitespace and '.'. All other ASCII characters are accepted although it is suggested that

the following characters are avoided if possible:

\ " % & + - \* / ^ < > [ ] ' @ { }

If any of these characters are used in a net name, a special syntax will be needed to plot any signal voltage on that net. This is explained in the "Output Data Names" section below. In addition the characters '[', ']', '%', '!' and '~' have a special meaning when used with XSPICE devices and therefore should be avoided at all times. The *name* is the circuit reference of the device. The first letter of this name determines the type of device as shown in the table below.

The Pin Names column in the following table is relevant to the vector name used for values of device pin current. See the "Output Data Names" section.

| Letter | No of pins | Device                            | Pin Names         |

|--------|------------|-----------------------------------|-------------------|

| А      | Any        | XSPICE devices                    | depends on device |

| В      | 2          | Arbitrary source                  | Ρ, Ν              |

| С      | 2          | Capacitor                         | P, N              |

| D      | 2          | Diode                             | P, N              |

| Е      | 4          | Voltage controlled voltage source | P, N, CP, CN      |

| F      | 2          | Current controlled current source | P, N              |

| G      | 4          | Voltage controlled current source | P, N, CP, CN      |

| н      | 2          | Current controlled voltage source | P, N              |

| I      | 2          | Fixed current source              | P, N              |

| J      | 3          | JFET                              | D, G, S           |

| к      | 0          | Coupling for inductors            | -                 |

| L      | 2          | Inductor                          | Ρ, Ν              |

| М      | 4          | MOSFET                            | D, G, S, B        |

| Ν      | -          | Not used                          | -                 |

| 0      | 4          | Lossy transmission line           | P1, N1, P2, N2    |

| Р      | -          | Not used                          | -                 |

| Q      | 3-5        | Bipolar transistor                | C, B, E, S, DT    |

| R      | 2          | Resistor                          | P, N              |

| S      | 4          | Voltage controlled switch         | P, N, CP, CN      |

| т      | 4          | Lossless transmission line        | P1, N1, P2, N2    |

| U      | -          | Not used                          | -                 |

| V      | 2          | Voltage source                    | Ρ, Ν              |

| W      | -          | Not used                          | -                 |

| х      | Any        | Subcircuit                        | -                 |

| Y      | -          | Not used                          | -                 |

| Z      | 3          | GaAs FET                          | D, G, S           |

|        |            | IGBT                              | C, G, E           |

To remove the naming restriction that this system imposes, Pulsonix Spice supports an extension to the above to allow the user to use any name for all devices. If the device letter is followed by a dollar '\$' symbol (by default but can be changed - see below), the remainder of the name following the '\$' will be used as the device name. E.g.:

Q\$TR23

will define a bipolar transistor with the name TR23. All output generated by the simulator will refer to TR23 not Q\$TR23. This mechanism will be disabled if HSPICE or PSPICE languages are specified.

### Simulator Controls

Instructions to the simulator other than device definitions and comments are referred to as *controls* and always begin with a period '.'.

Full documentation for the simulator controls, see the User s Guide.

## **Simulator Output**

#### The List File

Pulsonix-Spice produces a list file by default. This receives all text output except for the Monte Carlo log. This includes operating point results, model parameters, noise analysis results, sensitivity analysis results, pole-zero analysis results and tabulated vectors specified by .PRINT.

The list file is generated in the same directory as the netlist. It has the same name as the netlist but with the extension .OUT.

There are a number of options that control the list file output.

| Option name | Description                                                                                                                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMLOG    | Valid values:                                                                                                                                                                                                                      |

| Full        | All instance and model parameter values reported                                                                                                                                                                                   |

| Given       | All user specified model parameters and parameterised instance parameters                                                                                                                                                          |

| Brief       | Parameterised model and instance parameters                                                                                                                                                                                        |

| None        | None                                                                                                                                                                                                                               |

|             | Default = Given                                                                                                                                                                                                                    |

| EXPAND      | Flag. If specified, the netlist with all sub-circuits expanded will be output to the list file                                                                                                                                     |

| EXPANDFILE  | String. If specified the expand netlist will be output to the specified file rather than the list file                                                                                                                             |

| NOMOD       | Same as PARAMLOG=none. Model parameters will not be output                                                                                                                                                                         |

| WIDTH       | Page width in number of characters. (The list file is formatted assuming that it will be read or printed using a fixed width font such as Courier.) The default is 80 but any value may be used not just 80 and 132 as in SPICE 2. |

| OPINFO      | If set DC operating point info file <i>is</i> created for all analyses (except .SENS). Normally it is created only for .OP analyses                                                                                                |

#### The Binary Data File

The simulation data is stored in a binary data file. The format is proprietary to Pulsonix and is not compatible with SPICE 'raw' files.

The name and location of the binary file depends on configuration settings and in what

mode the simulator is run. The file is usually stored in a temporary location and is named according to the analysis type and appended with the extension .sxdat. E.g.tran1.sxdat, ac2.sxdat, dc3.sxdat etc. To save this data to your own location see the *Saving Data* section in the *Graphs & Probes* chapter of the Pulsonix Spice Users Guide.

Only Pulsonix-Spice can read the simulator's binary data file. When run from a schematic design, the file is automatically loaded and in fact it is not usually necessary to know anything about it except perhaps when it grows very large and fills up your disk. From the command shell you can explicitly load the data file when the run is complete. This can be done with the command shell menu **File**|**Data**|**Load....** After the data is loaded, the results can be plotted in the usual manner.

#### **Output Data Names**

For transient, DC and AC analyses, Pulsonix-Spice calculates and stores the circuit's node voltages and device pin currents and these are all given unique names. If using probing techniques with the Pulsonix schematic editor you don't usually need to know anything about the names used. However there are situations where it is necessary or helpful to know how these names are derived. An example is when compiling an expression relating voltages and currents to be used in a .PRINT control. Another is when plotting results created by simulating a netlist that was not generated using the schematic editor. The names used are documented in the following notes.

#### **Top Level Node Voltages**

The vector names used for node voltages at the top level (i.e. not in a subcircuit) are simply the name of the node used in the netlist.

#### Subcircuit Node Voltages

For nodes within a subcircuit, the name is prefixed with the subcircuit reference and a '.'. For example:

```

X1 N1 N2 N3 SubName

X2 N4 N5 N6 SubName

.SUBCKT 1 2 3 SubName

X3 N1 2 N3 SubName2

R1 VIN 0 1k

...

.ENDS

.SUBCKT 1 2 3 SubName2

V1 VCC 0 5

...

.ENDS

```

The internal node VIN in definition SubName referenced by X1 would be called X1.VIN. The same node referenced by X2 would be called X2.VIN. The node VCC defined in subcircuit SubName2 would be named X1.X3.VCC and X2.X3.VCC for X1 and X2 respectively.

#### Nodes with Non-standard Names

A non-standard node name is one that begins with a digit or which contains one or more of the characters:

\ " % & + - \* / ^ < > [ ] ' @ { }

These are legal but introduce problems when accessing the voltage data that they carry. The above characters can be used in arithmetic expressions so cause a conflict if used as a node name. In order to access the voltage data on a node so named, use the Vec() function:

```

Vec('node_name')

```

Example with .PRINT and node called V+

.PRINT TRAN {Vec('V+')}

A similar syntax is required when using the front end plotting commands.

#### **Device Pin Currents**

Device pin currents are named in the following form:

device\_name#pin\_name

For primitive devices (i.e. not sub-circuits) *pin\_name* must comply with the table defined in the Pulsonix-Spice Users Guide, in the *Device Library and Model Management*

Chapter, section *Simulator Device Pin Names*. For example the current into the collector of Q23 would be Q23#c.

The pin names for sub-circuits depend on whether the pinnames: specifier (see

"Subcircuit Instance" in the Pulsonix Spice Device Reference Manual) is included in the netlist entry for the device. If it is the pin current name will be the name listed after *pinnames:*. If it isn't then they are numbered in sequence starting from 1. The order is the same as the order they appear in the netlist device line. For example, if the subcircuit line is:

X\$U10 N1 N2 N3 N4 N5 LM324 pinnames: VINP VINN VP VN VOUT The current into the last pin (connected to N5) would be U10#VOUT

(Note that 'X\$' is stripped off).

If the netlist line is:

$$\rm x$U10\ N1\ N2\ N3\ N4\ N5\ LM324$$  The same current would be U10#5

## Internal Node Voltages

Some devices have internal nodes and the voltages on these are output by the simulator. These are named in a similar manner to pin currents i.e.

device\_name#internal\_node\_name

The *internal\_node\_name* depends on the device. For example, bipolar transistors create an internal node for each terminal that specifies a corresponding resistance parameter. So if the RE parameter is specified an internal node will be created called emitter.

## 16 Simulator Data Formats

## **Chapter 2. Simulator Devices**

## Overview

This chapter is an introduction to the "Analog Device Reference and the "Digital/Mixed Signal Device Reference".

The device reference chapters describe all simulator devices at the netlist level. The netlist consists of a list of component definitions, along with simulator commands, which the simulator can understand. Simple components, such as resistors just need a value to define them. Other more complicated devices such as transistors need a number of parameters to describe their characteristics.

The device references includes details of all device and model parameters. Using the schematic editor and model library you may not often need to read this section. Some of the devices, however, have advanced options not directly supported by the user interface. For example, many devices allow a local temperature to be specified. This requires the component value to be appended with TEMP=.... This device parameter and others are documented here.

Note that many parts either supplied with Pulsonix Spice or available from component manufacturers are implemented as subcircuits. These are circuit designs to simulate the behaviour of high level devices such as opamps. Pulsonix does not have an opamp device built in but use these *macro models* instead. Full documentation for these devices is beyond the scope of this manual but can sometimes be obtained from their suppliers.

### Using XSPICE Devices

Some devices are implemented as part of the XSPICE 'code modelling' framework. This framework introduces some new features at the netlist level not supported by standard SPICE devices. These new features are described in this section. Most of the devices that use this framework are digital or mixed signal devices and the reference for these can be found at "Digital/Mixed Signal Device Reference" However there are three all analog devices that are also XSPICE devices. These are:

- "Capacitor with Voltage Initial Condition"

- "Inductor with Current Initial Condition"

- "S-domain Transfer Function Block"

#### Vector Connections

Some models feature an arbitrary number of inputs or/and outputs. For example, an AND gate can have any number of inputs. It would be inflexible to have a separate model for every configuration of AND gate so a method of grouping connections together has been devised. These are known as *vector connections*. Vector connections are enclosed in square brackets. E.g. the netlist entry for an AND gate is:

Axxxx [ in\_0 in\_1 .. in\_n ] out model\_name

#### 18 Simulator Devices

The pins in\_0 in\_1 to in\_n form a single vector connection. Any number of pins may be placed inside the square brackets, in fact the same model may be used for devices with different numbers of inputs.

Some devices have a minimum and/or maximum number of pins that may be used in a vector connection. This is known as *vector bounds* and if they apply will be listed in the vector bounds column of the Connection Details table provided with every device definition.

To add vector connections to a schematic part, use the pin properties button on the Define Spice Type dialog. See the Device Library and Model Management chapter in the Pulsonix Spice User's Manual for details on how to do this.

#### **Connection Types**

In the device references that follow, each has a table titled "Connection Details". Each table has the column entries "Default type" and "Allowed types". The *type* referred to here is the type of electrical connection e.g. voltage, current, differential or single-ended. Some devices allow some or all of their connections to be specified with a range of types. For example, the analog-digital converter described later in *Device Reference* under *Analog-Digital Converter* has a single ended voltage input by default. However, using a simple modification to the netlist entry, an ADC can be specified with a differential voltage input or even a differential current. Changing the type of connection involves no changes to the .MODEL control, only to the netlist entry.

The following table lists all the available types. The modifier is the text used to alter a connection type at the netlist level. This is explained below

| Description                                             | Modifier |

|---------------------------------------------------------|----------|

| Single ended voltage                                    | % v      |

| Single ended current                                    | %i       |

| Differential voltage                                    | %vd      |

| Differential current                                    | %id      |

| Digital                                                 | %d       |

| Grounded conductance (voltage input current output)     | %g       |

| Grounded resistance (current input, voltage output)     | %h       |

| Differential conductance (voltage input current output) | %gd      |

| Differential resistance (voltage input current output)  | %hd      |

With the models supplied with Pulsonix Spice, only the first four in the above table are ever offered as options. The others are used but are always compulsory, and an understanding of their meaning is not necessary to make full use the system.

As well as *type*, all connections also have a *direction*. This can be *in*, *out* or *inout*. Voltage, current and digital connections may be *in* or *out* while the conductance and resistance connections may only be *inout*. Voltage inputs are always open circuit, current inputs are always short circuit, voltage outputs always have zero output impedance and current outputs always have infinite output impedance.

The conductance connections are a combined voltage input and current output connected in parallel. If the output is made to be proportional to the input, the connection would be a conductor with a constant of proportionality equal to its conductance, hence the name.

Similarly, the resistance connections are a combined current input and voltage output connected in series. If the output is made to be proportional to the input, the connection would be a resistor with a constant of proportionality equal to its resistance.

#### **Changing Connection Type**

If a model allows one or more of its connections to be given a different type, this can be done by preceding the connection entry with the appropriate modifier listed in the table above. For example if you wish to specify a 4 bit ADC with a differential voltage input, the netlist entry would be something like:

A1 %vd ANALOG\_INP ANALOG\_INN CLOCK\_IN [ DATA\_OUT\_0 DATA\_OUT\_1 DATA\_OUT\_2 DATA\_OUT\_3 ] DATA\_VALID ADC\_4

## Using Expressions

#### Overview

Expressions consist of arithmetic operators, functions, variables and constants and maybe employed in the following locations:

- As device parameters

- As model parameters

- To define a variable which can itself be used in an expression

- As the governing expression used for arbitrary sources

They have a wide range of uses. For example:

- To define a number of device or model parameters that depend on some common characteristic. This could be a circuit specification such as the cut-off frequency of a filter or maybe a physical characteristic to define a device model.

- To define tolerances used in Monte Carlo analyses.

- Used with an arbitrary source, to define a non-linear device.

#### Using Expressions for Device Parameters

Device or instance parameters are placed on the device line. For example the length parameter of a MOSFET, L, is a device parameter. A MOSFET line with constant parameters might be:

M1 1 2 3 4 MOS1 L=1u W=2u L and W could be replaced by expressions. For example

M1 1 2 3 4 MOS1 L={LL-2\*EDGE} W={WW-2\*EDGE}

Device parameter expressions must usually be enclosed with either single quotation marks ( ') double quotation marks ( ") or braces ( '{' and '}'). The expression need not be so enclosed if it consists of a single variable. For example:

.PARAM LL=2u WW=1u M1 1 2 3 4 MOS1 L=LL W=WW

#### Using Expressions for Model Parameters

The rules for using expressions for device parameters also apply to model parameters. E.g.

.MODEL N1 NPN IS=is BF={beta\*1.3}

#### Expression Syntax

The expression describing an arbitrary source consists of the following elements:

Circuit variables

- Parameters

- Constants.

Operators

- Functions

- Look up tables

These are described in the following sections

#### **Circuit Variables**

Circuit variables may only be used in expressions used to define arbitrary sources and to define variables that themselves are accessed only in arbitrary source expressions.

Circuit variables allow an expression to reference voltages and currents in any part of the circuit being simulated.

Voltages are of the form:

```

V(node_name)

```

Where *node\_name* is the name of the net carrying the voltage of interest.

Currennts are of the form:

```

I(source_name)

```

Where *source\_name* is the name of a voltage source carrying the current of interest. The source may be a fixed voltage source, a current controlled voltage source, a voltage controlled voltage source or an arbitrary voltage source. It is legal for an expression used in an arbitrary source to reference itself e.g.:

Implements a 100 ohm resistor.

#### Parameters

These are defined using the .PARAM control. See Pulsonix Spice Users Guide, Command reference section for more details. For example

```

.PARAM res=100

B1 n1 n2 V=res*I(B1)

```

Also implements a 100 ohm resistor.

For release 2 and later it is possible to put circuit variables in .PARAM controls. For example:

.PARAM VMult = { V(a) \* V(b) } B1 1 2 V = Vmult + V(c)

#### **Built-in Parameters**

A number of parameter names are assigned by the simulator. These are:

| Parameter name | Description                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| TIME           | Resolves to time for transient analysis. Resolves to 0 otherwise including during the pseudo transient operation point algorithm. |

| TEMP           | Resolves to current circuit temperature                                                                                           |

| HERTZ          | Resolves to frequency during AC sweep and zero in other analysis modes                                                            |

| PTARAMP        | Resolves to value of ramp during pseudo transient point algorithm.                                                                |

operating

#### Constants

Apart from simple numeric values, arbitrary expressions may also contain the following built-in constants:

| Constant name | Value Description         |                          |

|---------------|---------------------------|--------------------------|

| PI            | 3.14159265358979323846    | π                        |

| Ε             | 2.71828182845904523536    | e                        |

| TRUE          | 1.0                       |                          |

| FALSE         | 0.0                       |                          |

| ECHARGE       | 1.6021918e-19<br>coulombs | Charge on an electron in |

| BOLTZ         | 1.3806226e-23             | Boltzman's constant      |

If the simulator is run from the front end in GUI mode, it is also possible to access variables defined on the Command Shell command line or in a script. The variable must be global and enclosed in braces. E.g.

B1 n1 n2 V = V(n3, n3) \* { global:amp\_gain }

*amp\_gain* could be defined in a script using the LET command. E.g. "Let global:amp\_gain = 100"

#### Operators

These are listed below and are listed in order of precedence. Precedence controls the order of evaluation. So 3\*4 + 5\*6 = (3\*4) + (5\*6) = 42 and 3+4\*5+6 = 3 + (4\*5) + 6 = 29 as '\*' has higher precedence than '+'.

| Operator     | Description                           |

|--------------|---------------------------------------|

| ~!-          | Digital NOT, Logical NOT, Unary minus |

| ^ or **      | Raise to power                        |

| *,/          | Multiply, divide                      |

| +, -         | Plus, minus                           |

| >=, <=, ><   | Comparison operators                  |

| ==, != or <> | Equal, not equal                      |

| &            | Digital AND (see below)               |

|              | Digital OR (see below)                |

| &&           | Logical AND                           |

| II           | Logical OR                            |

#### **Comparison, Equality and Logical Operators**

These are Boolean in nature either accepting or returning Boolean values or both. A Boo lean value is either TRUE or FALSE. FALSE is defined as equal to zero and TRUE is defined as not equal to zero. So, the comparison and equality operators return 1.0 if the result of the operation is true otherwise they return 0.0.

The arguments to equality operators should always be expressions that can be guaranteed to have an exact value e.g. a Boolean expression or the return value from functions such as SGN. The == operator, for example, will return TRUE only if both arguments are *exactly* equal. So the following should never be used:

v(n1) = 5.0

v(n1) is never likely to be exactly 5.0. It may be 4.9999999999 or 5.00000000001 but only by fluke will it be 5.0.

These operators are intended to be used with the IF() function described below.

#### **Digital Operators**

These are the operators '&', '|' and '~'. These were introduced in release 1.0 as a simple means of implementing digital gates in the analog domain. Their function has largely been superseded by gates in the event driven simulator but they are nevertheless still supported.

Although they are used in a digital manner the functions implemented by these operators are continuous in nature. They are defined as follows:

| Expression     | Condition                                                                              | Result                                         |

|----------------|----------------------------------------------------------------------------------------|------------------------------------------------|

| out = x & y    | x <vtl or="" td="" y<vtl<=""><td>out = vl</td></vtl>                                   | out = vl                                       |

|                | x>vth AND y>vth                                                                        | out = vh                                       |

|                | x>vth AND vth>y>vtl                                                                    | out = (y-vtl)*(vh-vl)/(vth-vtl)+vl             |

|                | vtl <x< and="" vth="" y="">vth</x<>                                                    | out = (x-vtl)*(vh-vl)/(vth-vtl)+vl             |

|                | vtl <x< and="" vth="">y&gt;vtl</x<>                                                    | out = (y-vtl)*(x-vtl)*(vh-vl)/(vthvtl)<br>2+vl |

| out = x   y    | x <vtl and="" td="" y<vtl<=""><td>out = vl</td></vtl>                                  | out = vl                                       |

|                | x>vth OR y>vth                                                                         | out = vh                                       |

|                | x <vtl and="" vth="">y&gt;vtl</vtl>                                                    | out = vh-(vth-y)*(vh-vl)/(vth-vtl)             |

|                | vtl <x< and="" th="" vth="" y<vtl<=""><th>vtl<x< and="" vth="">y&gt;vtl</x<></th></x<> | vtl <x< and="" vth="">y&gt;vtl</x<>            |

|                | out = vh-(vth-x)*(vh-vl)/(vth-vtl)                                                     | out = vh-(vth-y)*(vth-x)*(vh-vl)/(vth-vtl)     |

| $out = \sim x$ | x <vtl< td=""><td>out = vh</td></vtl<>                                                 | out = vh                                       |

|                | x>vth                                                                                  | out = vl                                       |

|                | vtl <x<vth< th=""><th>out = (vth-x)/(vth-vtl)*(vh-vl)+vl</th></x<vth<>                 | out = (vth-x)/(vth-vtl)*(vh-vl)+vl             |

| Whore          |                                                                                        |                                                |

Where:

vth = upper input threshold

vtl = lower input threshold

vh = output high

vl = output low

These values default to 2.2, 2.1, 5 and 0 respectively. These values are typical for high speed CMOS logic (74HC family). They can be changed with four simulator options set by the .OPTIONS simulator control. These are respectively,

LOGICTHRESHHIGH, LOGICTHRESHLOW, LOGICHIGH, LOGICLOW

To change the lower input threshold to 1.9, add the following line to the netlist:

.OPTIONS LOGICTHRESHLOW=1.9

To find out how to add additional lines to the netlist when using the schematic editor, refer to "Adding Extra Netlist Lines" in the Pulsonix-Spice Users Guide.

#### **Functions**

| Function | Description                                          |

|----------|------------------------------------------------------|

| ABS(x)   | Magnitude of x. if x>=0 result=x otherwise result=-x |

| ACOS(x)  | Arc cosine. Result is in radians                     |

| ACOSH(x) | Inverse COSH                                         |

| ASIN(x)          | Arc sine. Result is in radians                                          |

|------------------|-------------------------------------------------------------------------|

| ASINH(x)         | Inverse SINH                                                            |

| ATAN(x)          | Arc tangent. Result is in radians                                       |

| ATAN2(x,y)       | =ATAN(x/y). Valid if y=0. Result in radians                             |

| ATANH(x)         | Inverse TANH                                                            |

| COS(x)           | Cosine of x in radians                                                  |

| COSH(x)          | Hyperbolic cosine                                                       |

| DDT(x)           | Differential of x with respect to time                                  |

| EXP(x)           | ex                                                                      |

| FLOOR(x)         | Next lowest integer of x.                                               |

| IF(cond, x, y)   | if cond is TRUE result=x else result=y                                  |

| IFF(cond, x, y)  | As IF(cond, x, y)                                                       |

| LIMIT(x, lo, hi) | if x <lo else="" if="" result="lo" x="">hi result=hi else result=x</lo> |

| LN(x)            | Log to base e of x. If $x < 10_{-100}$ result=-230.2585093              |

| LOG(x)           | Log to base 10 of x. If $x < 10_{-100}$ result=-100                     |

| LOG10(x)         | Log to base 10 of x. If $x < 10_{-100}$ result=-100                     |

| MAX(x, y)        | Returns larger of x and y                                               |

| MIN(x,y)         | Returns smaller of x and y                                              |

| PWR(x,y)         | $ \mathbf{x} _{\mathbf{y}}$                                             |

| PWRS(x,y)        | if x>=0 $ x _y$ else $- x _y$                                           |

| SDT(x)           | Integral of x with respect to time                                      |

| SGN(X)           | If x>0 result = 1 else if x<0 result = -1 else result = 0               |

| SIN(x)           | Sine of x in radians                                                    |

| SINH(x)          | Hyperbolic sine                                                         |

| SQRT(x)          | if $x \ge 0 \forall x \text{ else } \forall -x$                         |

| STP(x)           | If $x \le 0$ result = 0 else result =                                   |

| TAN(x)           | Tangent of x in radians                                                 |

| TANH(x)          | Hyperbolic tangent                                                      |

| U(x)             | as STP(x)                                                               |

| URAMP(x)         | if x<0 result =0 else result = x                                        |

|                  |                                                                         |

#### **Monte Carlo Distribution Functions**

To specify Monte Carlo tolerance for a model parameter, use an expression containing one of the following 12 functions:

| Name    | Distribution           | Lot? |

|---------|------------------------|------|

| GAUSS   | Gaussian               | No   |

| GAUSSL  | Gaussian               | Yes  |

| UNIF    | Uniform                | No   |

| UNIFL   | Uniform                | Yes  |

| WC      | Worst case             | No   |

| WCL     | Worst case             | Yes  |

| GAUSSE  | Gaussian logarithmic   | No   |

| GAUSSEL | Gaussian logarithmic   | Yes  |

| UNIFE   | Uniform logarithmic    | No   |

| UNIFEL  | Uniform logarithmic    | Yes  |

| WCE     | Worst case logarithmic | No   |

| WCEL    | Worst case logarithmic | Yes  |

A full discussion on the use of Monte Carlo distribution functions is given in the Pulsonix-Spice Users Guide.

#### Look-up Tables

Expressions may contain any number of look-up tables. This allows a transfer function of a device to be specified according to - say - measured values without having to obtain a mathematical equation. Look-up tables are specified in terms of x, y value pairs which describe a piece-wise linear transfer function.

Look up tables are of the form:

TABLE[ xy\_pairs ]( input\_expression )

Where:

| xy_pairs | A sequence of comma separated pairs of constant values that define       |

|----------|--------------------------------------------------------------------------|

|          | the input and output values of the table. For each pair, the first value |

|          | is the x or input value and the second is the y or output value. Only    |

|          | explicit numberic constants may be used. Even internal constants         |

| such     | as PI may not be used.                                                   |

|          |                                                                          |

*input\_expression* Expression defining the input or x values of the table.

#### Example

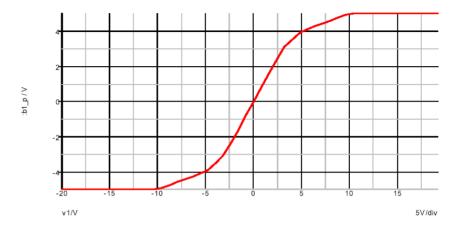

The following arbitrary source definition implements a soft limiting function

B1 n2 n3 v=table[-10, -5, -5, -4, -4, -3.5, -3, -3, 3, 3, 4, 3.5, 5, 4, 10, 5] (v(N1))

and has the following transfer function:

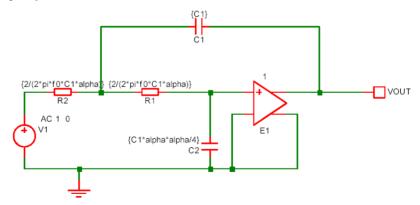

It is possible to assign expressions to component values which are evaluated when the circuit is simulated. This has a number of uses. For example you might have a filter design for which several component values affect the roll off frequency. Rather than recalculate and change each component every time you wish to change the roll of frequency it is possible to enter the formula for the component's value in terms of this frequency.

The above circuit is that of a two pole low-pass filter. C1 is fixed and R1=R2. The design equations are:

R1=R2=2/(2\*pi\*f0\*C1\*alpha)

C2=C1\*alpha\*alpha/4

where f0 is the cut off frequency and alpha is the damping factor.

The complete netlist for the above circuit is:

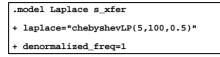

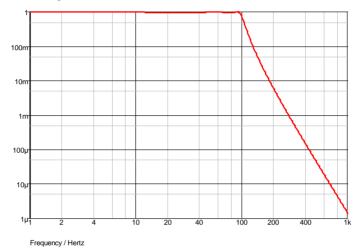

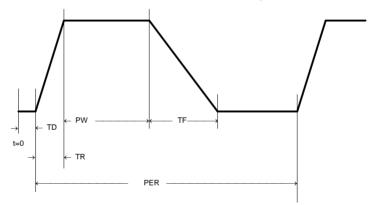

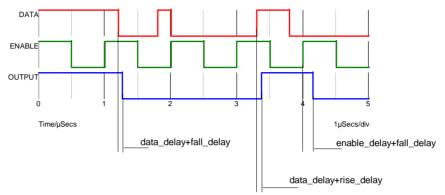

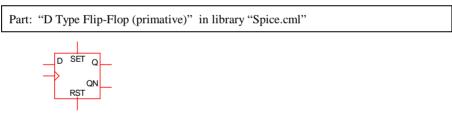

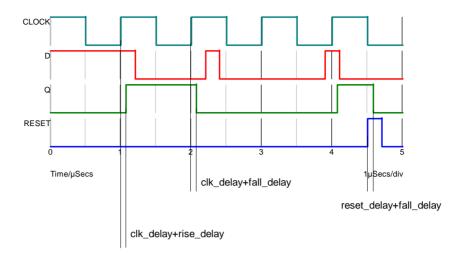

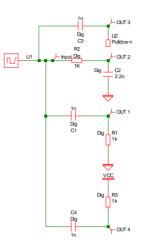

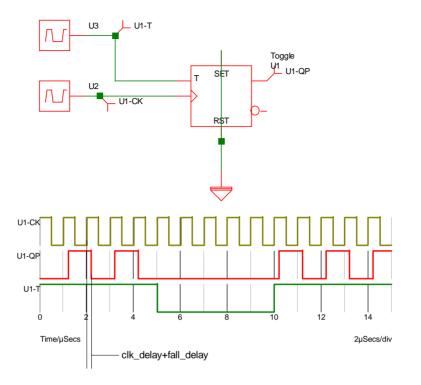

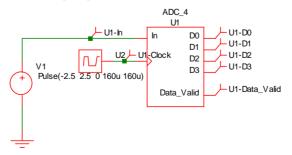

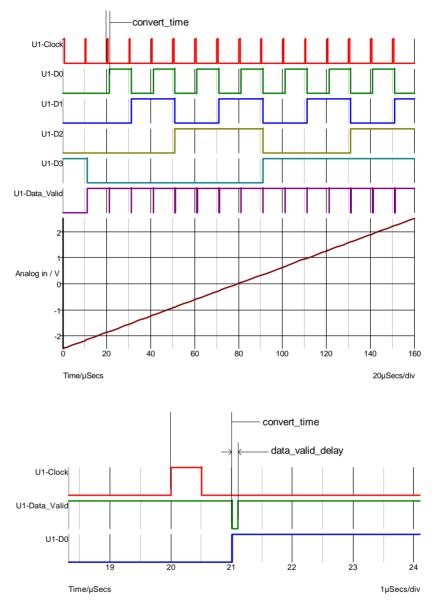

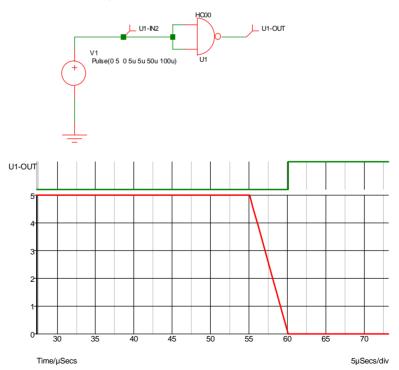

V1 V1\_P 0 AC 1 0