# PULSONIX

# Pulsonix Design System V6.0 Update Notes

#### **Copyright Notice**

Copyright © WestDev Ltd. 2000-2009 Pulsonix is a Trademark of WestDev Ltd. All rights reserved. E&OE

Copyright in the whole and every part of this software and manual belongs to WestDev Ltd. and may not be used, sold, transferred, copied or reproduced in whole or in part in any manner or in any media to any person, without the prior written consent of WestDev Ltd. If you use this manual you do so at your own risk and on the understanding that neither WestDev Ltd. nor associated companies shall be liable for any loss or damage of any kind.

WestDev Ltd. does not warrant that the software package will function properly in every hardware software environment.

Although WestDev Ltd. has tested the software and reviewed the documentation, WestDev Ltd. makes no warranty or representation, either express or implied, with respect to this software or documentation, their quality, performance, merchantability, or fitness for a particular purpose. This software and documentation are licensed 'as is', and you the licensee, by making use thereof, are assuming the entire risk as to their quality and performance.

In no event will WestDev Ltd. be liable for direct, indirect, special, incidental, or consequential damage arising out of the use or inability to use the software or documentation, even if advised of the possibility of such damages.

WestDev Ltd. reserves the right to alter, modify, correct and upgrade our software programs and publications without notice and without incurring liability.

Microsoft, Windows, Windows NT and Intellimouse are either registered trademarks or trademarks of Microsoft Corporation.

All other trademarks are acknowledged to their respective owners.

Pulsonix, a division of WestDev Ltd.

Printed in the UK Issue date: 23/07/09 iss 2

#### **Pulsonix**

Oak Lane Bredon, Tewkesbury Glos, GL20 7LR United Kingdom

Phone +44 (0)1684 773881 Fax +44 (0)1684 773664 Email info@pulsonix.com Web www.pulsonix.com

## **Contents**

| CHAPTER 1. VERSION 6.0 UPDATE SUPPLEMENT              | 5  |

|-------------------------------------------------------|----|

| Installing the New Version of Pulsonix                | 5  |

| Licensing                                             | 5  |

| Automatically Check For Updates                       |    |

| Dual Screen Support                                   |    |

| View All On Open Design                               |    |

| Definable Environment Variable Character              |    |

| Additional Library Report – Check for Duplicate Items | 8  |

| Library Documenter                                    | 9  |

| Mapping Multiple PCB Pads to same Schematic Pin       |    |

| Part & Symbol Summary Information                     | 12 |

| Variant Text, Callouts and Attributes                 |    |

| Display of Variant Components                         |    |

| Filter Warnings                                       |    |

| Import Option Layer Mapping                           |    |

| Full ECO Back to the Schematic                        |    |

| Enabling Full Back ECO                                |    |

| Component Bin Changes                                 |    |

| Schematic Safe Mode                                   |    |

| Schematic Connect Guides                              |    |

| Embedded Views                                        |    |

| Spacings/Styles By Area                               | 26 |

| Using Area Based Spacings/Styles                      |    |

| Setting the Default Routing Styles for the Area       |    |

| Net Styles                                            | 29 |

| Disconnect Track End in Select Mode                   |    |

| Auto Weld Selection                                   |    |

| Footprint Wizard - Rotate Breakouts by Quadrant       | 33 |

| Track Edit Improvements                               |    |

| Track/Via Pushing                                     |    |

| Pull Tight Tool                                       |    |

| Pull Tight during Insert Track                        | 34 |

| Auto Finish                                           |    |

| Component Body and Clearance Areas                    | 35 |

| Net Class Track Length Difference                     |    |

| Segment Mode Menu Changes                             | 37 |

| Thermal Rules – Alternative Spoke Rotations           |    |

| Alternative Thermal Gap Shape                         |    |

| Re-pouring Protel Templates                           | 38 |

| Templates – Set Pour Order                            |    |

| Negative Text on Power Planes                         |    |

| Plot Groups in CAM Plot                               | 40 |

| Suppress Unconnected Lands                            |    |

| Case-sensitive Drill IDs                              |    |

| Checking between Hatch Lines                          |    |

| Delete Testpoints – Locked Against Automatic Removal  |    |

| Mirror Pad Stack                                      |    |

| Library Changes                                       | 44 |

## Chapter 1. Version 6.0 Update Supplement

## Installing the New Version of Pulsonix

It is recommended that you back-up all libraries, designs, technology files, profile files and report files before installing the latest version. Other than for any technical reason, this is good working practice, although you should already have a backup of this data!

To install Pulsonix, insert the CD or double-click on the download executable and wait for a short time. The Autorun facility will start the installation procedure. Follow the on-screen commands from the install wizard. You can install Pulsonix 6.0 on top of your existing installation or along side if you prefer; however, you do not need to uninstall the old version first.

## Licensing

If you are already using an earlier version of Pulsonix you will require a new license for Version 6.0. This will be supplied to you by email under the contract conditions of your current maintenance agreement.

For existing users, it is recommended that you save the new license and overwrite the existing one. When requested during installation, simply click the No Change In Licensing check box on the licensing page of the installation wizard. The **License Manager** can be used to add new licenses and make changes to network licensing after the installation has been completed.

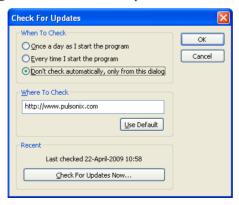

## **Automatically Check For Updates**

You can now check for available updates on the Pulsonix web site using a new option from the **Help** menu, **Check For Updates...** When selected, a dialog is displayed, this allows you to set up when you want to check for updates and where to check. It also allows you to force a check now. This will automatically direct you to the Pulsonix Updates page from where you can login and download the latest patch available.

If a patch isn't available, the dialog will report that none are available at this time. Before installing a new patch, ensure that Pulsonix isn't running, if it is, it must be closed.

## **Dual Screen Support**

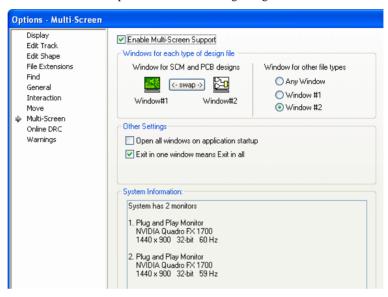

Support for dual screens has been added to V6.0. This includes Pulsonix options for Cross Probing, communications between Schematic and PCB designs on different screens, forward and backward annotation, dialog and window positioning and toolbar position memory.

Use the **Multi-Screen** page of the **Options** dialog to change how the application arranges separate instances across multiple monitors or on a single large monitor.

Select the **Enable Multi-Screen Support** check box to turn on this operation. With this enabled, two instances of the application will work together to arrange your files so you can easily work on Schematic designs on one screen, and PCB designs on the other. Each instance will have its own menus and toolbars and work independently, but will share information when they need to.

#### Using the Multi-screen dialog options

#### Windows for each type of design file

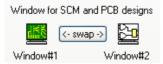

This setting shows which window is used for each design type. Although it doesn't really matter which way round they are, instance #1 is the one that will be launched first if you run Pulsonix with no designs open.

The small picture shows which design type will be displayed in which instance. To swap them round, simply click the **Swap** button.

#### Windows for other file types

As well as Schematic and PCB designs, Pulsonix is used to edit all your library items (Parts, Footprints, etc). You can choose where these should be opened for editing. You can choose either of the two specific program instances, for example you may wish to always edit library

items in the same instance as your Schematic designs, or you can allow them to be opened in the instance in which the editing action takes place.

#### Other Settings

#### Open all windows on application startup

With this checked, both instances of the program will be started when you launch Pulsonix. With it unchecked, launching Pulsonix will either start instance #1 (if no designs are open), or if you are opening a particular design file then it will launch the instance for that type of file.

There is no recommended setting for this switch, it simply depends on how you prefer to work, the default setting is on (checked).

#### Exit in one window means Exit in all

Check this box to make both instances close down if you close one of them. This makes them work more like a 'pair', but again it is simply related to how you want it to work.

The default setting for this switch is on (checked).

#### **System Information**

This panel shows any information relating to your system display configuration that the program has been able to report.

```

System Information:

System has 2 monitors

1. Plug and Play Monitor

NVIDIA Quadro FX 1700

1440 x 900 32-bit 60 Hz

2. Plug and Play Monitor

NVIDIA Quadro FX 1700

1440 x 900 32-bit 59 Hz

```

#### Synchronise In Multi-Screen Mode

When you are working in multi-screen mode, **Synchronise Designs** has to work across the two instances so that information about the Schematic and PCB are shared between the two. Depending on which changes need to be applied, and the direction in which you choose to apply them, Synchronise may display its various dialogs in one or other screen, or sometimes both.

Consider for example the situation where you have a Schematic and PCB design 'pair' open, the PCB design has Back Annotation changes waiting to be applied to the Schematic, and you have also connected a new component into the Schematic so those changes need to be applied to the PCB. If you invoke Synchronise Designs from the Schematic instance, it will detect the fact that the chosen PCB design is already open in the other instance. If the PCB has been modified, you will be prompted to save the changed PCB design to disk so the Schematic instance can read it. The back annotation data from the PCB design file will then be applied to the Schematic in the Schematic instance. At the same time a copy of the same Schematic design will be used in the PCB instance to carry out the 'normal' Synchronise sequence of Back Annotation followed by Forward Design Changes. The designs in both instances will thus be Synchronised by applying the appropriate set of changes in each instance.

To run Synchronise in Multi-Screen mode, you can choose Synchronise from either Schematic or PCB as usual. Depending on whether changes have been made to your designs since they were last saved, you may be prompted to save modified designs so the up-to-date copy can be read in the other instance. For the duration of the Synchronise operation, the design in the 'other' instance may be placed in 'read only' mode so that the controlling instance can access the design data, so you may notice the window caption changing to say 'View Only' and a number of the toolbar and menu options becoming greyed-out. The design will be returned to its normal state on exit from Synchronise.

## View All On Open Design

There is a new check box on the **Options** dialog under **Display**. **'View All' On Opening Designs**, this will execute a **View All** command whenever you open a design file.

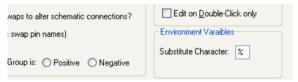

#### **Definable Environment Variable Character**

You can set the character to be used for delimiting environment variables in strings (the default is %). Previously this was hardwired into Pulsonix and not available for changing. Set it on the **Options** dialog under **General** and **Environment Variables**.

## Additional Library Report - Check for Duplicate Items

There is a new radio button on the report dialogs available in the **Library Manager** dialog to **Check For Duplicate Items**. This option scans all enabled libraries/folders and checks for Parts, Symbols, Doc Symbols or Footprints that exist in more than one library.

## **Library Documenter**

You can now document your Parts library with full graphical pictures of symbols and footprints as well as all Part detail information.

Select the **Report** button from the **Library Manager** option, **Parts** page.

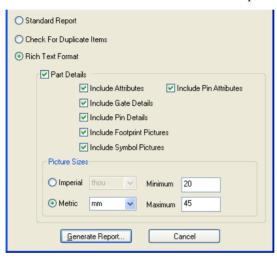

Select the **Rich Text Format** radio button to enable this option.

Select Part Details to enable the subsequent choices within it. With this box unchecked, a list of selected Parts only will be produced.

You are able to specify the Minimum and Maximum size of the graphic symbol pictures added to the document, this ensures they aren't too small or too large. The Imperial and Metric radio buttons allow you to specify the min and max picture size units.

When run, this report will produce an Rich Text Format (RTF) file. This can be read into your default documentation editor, such as Microsoft Word or Word Perfect.

An example report might look like the one below:

## Mapping Multiple PCB Pads to same Schematic Pin

You can now map one Schematic pin to many PCB pins using the Part Editor.

This feature allows you to model certain types of Component that have 'internal' connections within the Component itself, or those that have multiple pins that need to be assigned to the same net. This is an alternative method to connecting pads together in the footprint by adding to the same net or using wires. The advantage of this method is that it means the footprint definition can remain neutral and generic, where the Part definition is made specific to a device.

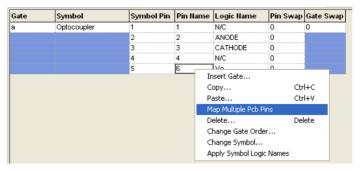

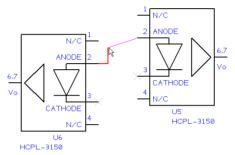

These mappings are made in the **Part Editor**. You will need to edit the Part that requires this mapping. On the **Gates** page, right click on the appropriate **Pin Name** cell and then select **Map Multiple Pcb Pins** from the context menu. This will turn the cell into an edit box instead of a drop down list to enable you to enter a list of PCB pin numbers. Type the Pin Numbers required into the list.

When edited, the Pin Name cell may look something like this for example:

| Symbol      | Symbol Pin | Pin Name | Logic Name |

|-------------|------------|----------|------------|

| Optocoupler | 1          | 1        | N/C        |

|             | 2          | 2        | ANODE      |

|             | 3          | 3        | CATHODE    |

|             | 4          | 4        | N/C        |

|             | 5          | 6,7      | Vo         |

The list can be separated in two ways depending on how you want them to behave in the PCB:

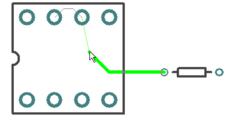

Separated with commas (to assign all the PCB pads to the same net, with connections in the PCB that need to be routed). When used in the PCB design, all the pads connected are displayed and can be routed to like the example below:

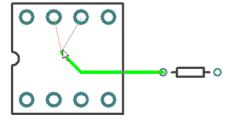

Or separated with plus signs (to assign them to the same net, but indicating that the pins are connected internally within the component and do not all need to be routed). However, when used in the PCB design, when routing close to an 'associated' pin, it will optimise to that net indicating a legal routing target as shown in the example below:

Note: If you want to use Alphanumeric Names, these names must first be added on the Pins page.

### **Part & Symbol Summary Information**

Additional **Document Summary** information is now saved with each Library Symbol and Part in the library.

The **Last Saved Date** was already held as the library item **Version**, but now the **Author**, **Comments**, **Last Saved By** and **Creation Date** are remembered.

These fields can be seen using the **Document Properties** option from the **File** menu when editing the Library Symbols or Parts, (this was previously greyed out for Parts). The **Keywords**, **Title** and **Subject** fields are disabled in this dialog. The **Comments** field is sufficient for library items.

You can use the **Report Maker** to report all of these fields, both in a library, and in the Parts and Symbols used within a Schematic or PCB design.

#### Variant Text, Callouts and Attributes

#### **Variants Text**

The ability to add text, specific to particular design variants is now supported.

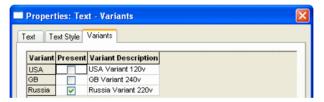

To use text variants, create design **Variants** using the **Variants Manager** and switch to a variant. In the design, add your text and position as required. Select the text and select **Properties** from the context menu. On the **Variants** page, select whether that text string will be **Present** or not on the selected variant. A description of the variant is also displayed for confirmation.

#### **Variants Text Callouts**

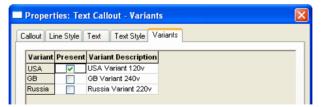

**Text Callouts** can be defined as variant specific. To do this, use the **Properties** dialog, **Variants** page and select the check box to show whether the callout is **Present** or not.

Text callouts that reference variant design attributes using attribute substitution will also not display or plot for variants in which the attribute is not present.

#### Variant Attributes

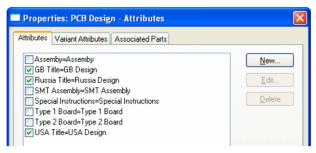

An additional **Variant Attributes** tab on the **Design Properties** dialog allows design attributes to be enabled/disabled for the defined variants in a Schematic or PCB design or Profile.

To use Variant Attributes, the attribute name must first be defined in the Design Properties dialog under Attributes.

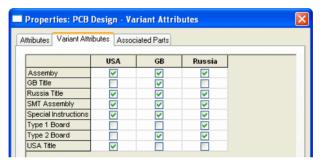

The Variant Attribute page in **Design Properties** is now used to define whether the Attribute is **Present** or not in the selected variant.

The table lists all design level attributes down the left hand side with each design variant shown as column heading across the top.

The check boxes indicate whether the design attribute named in that row is to appear in the design variant named in that column. Note that to actually be displayed on screen the attribute must also be checked as displayed under the Attributes tab. When there is a current variant active in the design only design attributes chosen to be shown for that variant will be listed under the Attributes tab.

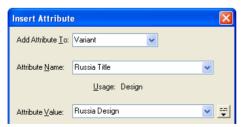

By default, when first added, a design attribute is shown in all variants. To remove it from a given variant uncheck the appropriate check box. Note that it is possible to add a new attribute exclusively to the current variant (if one is active) by using the Insert Attribute option and choosing Variant as the Add Attribute To setting selected from the drop down list.

For any changes made to the Variant Attributes or Attributes tab to be reflected in the other, without first closing the dialog, the **Apply** button must be clicked.

Attribute positions for **Design Attributes** defined as not present in the current variant will not be displayed or printed and will be excluded by the CAM Plot option in accordance with the variant settings of the defined plots.

Where design attributes are listed, those not present in the current variant will be omitted from the list.

### Display of Variant Components

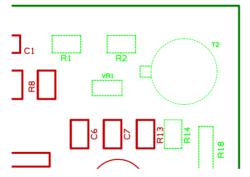

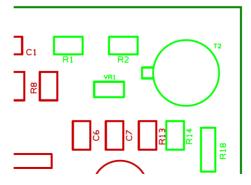

Variant component shapes can now be (optionally) drawn and plotted using the variant line style defined in the **Design Settings** dialog under **Variants** style.

The selection for this option is on the **Technology** dialog under **Layer Class** and **Variant Components** for a selected **Layer Class**.

When selected, the colour plot (and screen) will be drawn using the Variant style, in our example, a dotted style:

As a comparison, the colour plot below is shown using the Not Fitted colour only.

## **Filter Warnings**

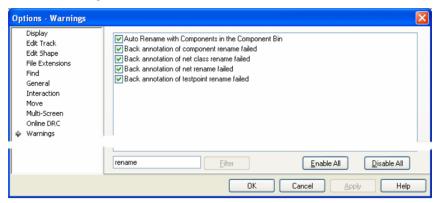

From within the **Options** dialog and **Warnings**, you can now filter the list of warnings. This will help reduce the list of Warnings displayed in the list to make the ones you are interested in more visible. In the Filter box, type a word which appears in the warning string. For example rename will give you just the warnings which contain the string rename. All standard wildcards are acceptable.

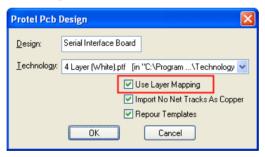

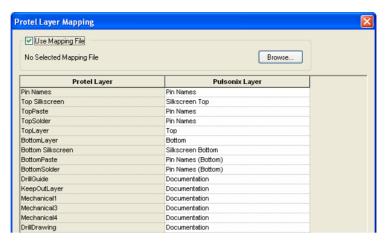

## Import Option Layer Mapping

When you are importing PCB Designs and Footprints from other EDA systems you can now map their original layers to Pulsonix layers. This saves you having to rename the layers later on manually. This option is only available if you select a Technology File and enable the Use Layer Mapping option via the check box.

Once you have mapped the layers you can save the mapping to a file using the **Save Mapping** button.

The mapping files can be used in the **Data Transfer Wizard** but must have been set up via the **Import xxx System** dialog (xxx being the source system product displayed).

#### **Full ECO Back to the Schematic**

#### **Enabling Full Back ECO**

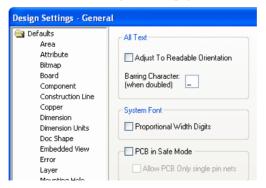

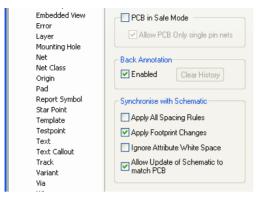

If you do want to make engineering changes (ECOs) in the PCB, you can now treat the PCB design as the master and use **Synchronise Designs** to update the Schematic.

#### To set up a PCB design as the master

- Synchronise the two designs first to ensure they match (select the option from the Tools menu).

- In the PCB design, take it out of Safe Mode by checking the PCB in Safe Mode box on the Design Settings dialog, General page.

Enable Backward Design Changes by checking the Allow Update of Schematic to match PCB box for the PCB design on the Design Settings dialog, General page.

In the Schematic, on the **Design Settings** dialog, **General** page, for the **Schematics Safe Mode** entry. The default mode in the standard Technology files is for it to be unchecked (not in Safe Mode).

## ► To apply PCB changes to the Schematic

- Make the engineering changes to the PCB design and use Synchronise Designs to update the **Schematic** with the changes.

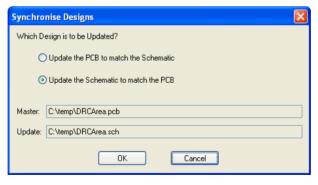

- When performing the **Synchronise Designs**, you are presented with a dialog from which to define the design to update.

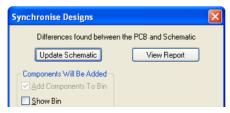

Once **OK** is pressed, you can then proceed to the standard **Synchronise Designs** dialog. This now shows the **Update Schematic** button to show that this is the design type being updated.

Any new Components added will appear in the **Used** section of the component bin in the schematic design.

Some changes may not be able to be made to the Schematic design, for example, when the change is in a multiply instanced hierarchical block. You will be warned if changes could not be made and will have to either change the PCB design a different way, or change the Schematic design so that the updates can be made.

#### The difference between a full back ECO and Reverse Engineer

In principle, running a full back ECO is the equivalent of running a Forward Design Change, but obviously the other way around. Whereas, running Reverse Engineer is the equivalent of running a Translate To PCB (but in reverse). However, the Reverse Engineer option will also allow you to automatically place the components and route the connections.

#### Component Bin Changes

As shown above in the previous section, part of the Backwards ECO product changes involves changing the Used section of the Component Bin. This is now underlined to make it clearer.

For Schematic designs in SCM Safe mode, the scope of a Gate (on a multi-gated Part), Testpoint or Connector in the bin will be shown if its pins are on local nets within a block. The scope is the name of the block instance, and it indicates that the gate can only be dragged onto a page within this block instance. You will not be able to drag it onto a page where any of its nets are not in scope.

In the example below, C2 is shown to be in scope in block B1.

```

USED ITEMS:

C2 - C [scope: B1]

-- U3 - TMS320C2802GGMA

Gate a - tms320c2802ggma 1.1

U6 - HCPL-3150

```

Single pin items in the bin that are on a net now show the name of the net. This makes it easier to place the correct Connector pin in Schematic, or the correct Testpoint in the PCB. For example, if you run the **Auto-Insert Testpoint** option in PCB and add the new testpoints to the bin.

In the example below, under the **Connectors:** heading, **PL1 pin 1** is shown to be attached to the net **CLK** and in scope on block B1.

```

USED ITEMS:

-- U3 - TMS320C2802GGMA

Gate a - tms320c2802ggma 1.1

U6 - HCPL-3150

Connectors:

-- PL1 [1] - 2510-5002

Pin 1 [CLK] [scope: B1]

```

#### Schematic Safe Mode

As a pre-cursor to Backwards ECO, you can now put your Schematic design into Safe Mode using the new check box option in **Design Settings** and the **General** tab. This mode is slightly different to that of the PCB version in that it does not allow Component, Testpoint and Net renames whereas the PCB equivalent does, (these items are allowed in PCB safe mode because you can use the Back Annotation feature to pass them to the Schematic design).

In Schematics, in this mode, you can drag connected items into the **Used** section of the Component Bin.

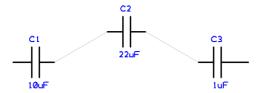

#### Schematic Connect Guides

Connect Guides in the Schematic design are the same as Unrouted Connections in PCB. In the previous release you could see these lines when moving Components after using the **Reverse Engineer** option, but they disappeared when the move finished.

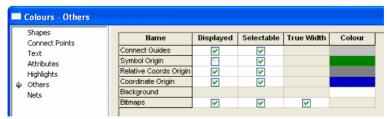

To make the new Backwards ECO changes easier to view in the Schematic, these lines can now be displayed all the time by switching on Connect Guides in the Others tab of the Colours dialog.

A connect guide is a thin line drawn from any pin that does not have a connection attached (and does not display its net name) to the closest node on its net on the same page. If no other node is on this page, no guide is drawn.

Switching them off in the Colours dialog will remove them all from the design view, and switching them on will re-generate them all.

You can double click to edit them directly to produce 'real' connections, or route them using the existing option Route Selected Connections.

You can also find them using the **Find** browser under a new category of **Connect Guide**.

#### **Embedded Views**

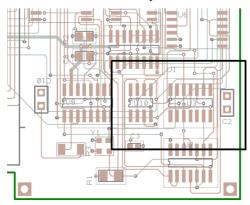

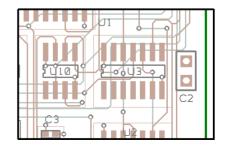

The Embedded Views option enables you to insert embedded design views into Pulsonix Schematic and PCB designs and into Profile files. These additional views of your design which will enable you to annotate various aspects of the design.

#### **Using Embedded Views**

#### ► To add embedded views

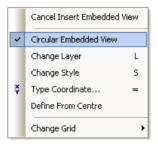

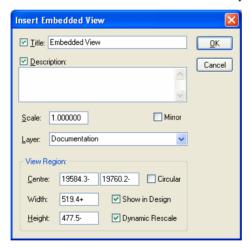

- To add an Embedded View, select **Embedded View** from the **Insert** menu. This will allow you to draw a region (rectangle or circle) around the area of interest in the

- With the modal cursor displayed, you can select options from the context menu.

The view must be named using the dialog presented. You cannot move it until it has been named. Various parameters can also be defined for it at this time or left until later. The scale of the view will be set to 1:1 by default.

The shape created is then added to the design so that you may then position it at the required location.

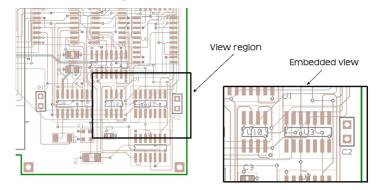

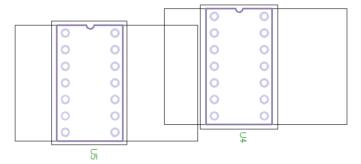

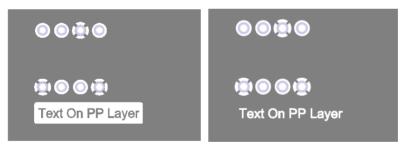

5. In the illustration below, the main design is shown on the left side and the embedded view shown on the right side.

## **▶** To modify embedded views

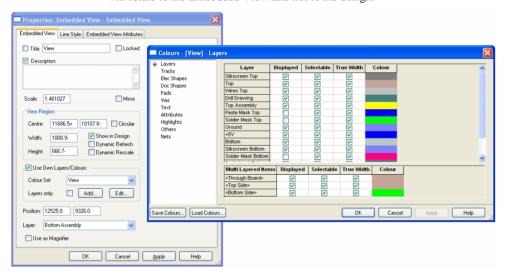

1. Embedded views can be modified by selecting the view area (or the existing design view area) and selecting **Properties** from the context menu.

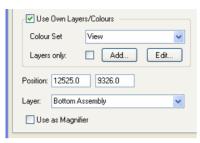

By default, the colours used in the embedded view are the same as those used in the design. If you wish to change them, you can select the Use Own Layers/Colours check box on the Properties dialog.

You can select an alternative colour set if one has been created previously for another Embedded View. If not, you are prompted to create a new one by clicking the Add button.

- By default, the name of the colour set will be the same as the Embedded View, but you can enter a different name if you prefer. Press the **OK** button to proceed.

- Now you can access the Colours dialog by using the Edit button. This colour set will relate to the Embedded View and not to the design.

- Choose the colours required in the Embedded View and press **OK**. Once you press **OK** on the **Properties** dialog, the colours will be applied. You can edit these colours at any time by pressing the Edit button again.

- Like the Pulsonix design, you can Save/Load these colour files.

#### Using the Embedded Views Properties dialog

#### Title

This shows the title (or name) of the Embedded View. It may be edited but must remain unique across the design.

#### **Description**

This shows an optional description. It may be edited and can be multi-line.

Either or both of Name and Description may be displayed as visible attributes alongside the Embedded View in the design by checking their adjacent checkboxes.

#### Locked

Use this to lock the Embedded View from future changes. Once the Embedded View has been correctly set up, lock it to avoid accidentally altering it.

#### Scale

Specifies the scale factor that the Embedded View will be displayed, relative to the main design.

#### Mirror

Check this for the Embedded View to show a mirror image of its region.

#### Laver

Displays and used to change the layer on which the Embedded View appears. Note: an Embedded View can only be placed on a non-electrical layer.

#### **Position**

Shows the position of the selected Embedded View using the current design units. If it is rectangular, this will be its lower left corner, if circular, it will be its centre point.

Type in a new position to move the Embedded View. If more than one Embedded View is selected and they have different positions, [Different] will be shown.

#### View Region

This section of the dialog defines the region of the design that will be displayed within the Embedded View. Centre specifies the point around which the region is centred. Width, **Height** and **Diameter** define the extents of the region depending on whether it is rectangular or circular. Editing these values will change the targeted region (from the shape centre).

It is also possible to change this region interactively (as you can you any regular shape), by directly moving or resizing the displayed region of the Embedded View in the design, or by panning and zooming within the actual Embedded View itself.

#### Show In Design

Check this to show, as well as the Embedded View itself, its View Region as a frame or circle in the design. The View Region is a fully functional shape and may be selected, moved and resized to change the viewed region.

#### Dynamic Refresh

Check this option if you want the Embedded View to dynamically refresh as its View Region is moved around the design providing a moving image display of the design underneath it.

#### **Dynamic Rescale**

This determines the effect of changes in size to the Embedded View or its View Region on each other. If unchecked, when either the Embedded View or its View Region is resized the other will resize about it centre point to match the new size and the scale factor will remain constant. When checked and the Embedded View or its View Region is resized, the other, rather than resizing as well, will adjust its scale factor to accommodate the new size thus leaving its own dimensions unchanged as far as a possible. Note however, that when a rectangular Embedded View is being used, changes in shape will inevitably have an affect on the aspect of other.

#### Use Own Lavers/Colours

The Use Own Lavers/Colours option on the Properties dialog allows the Embedded View to display a different set of visible items and/or colours to those displayed in the actual design. Once this is checked, you are able to define a colour set containing display information specific to the selected Embedded Views.

It is possible to share a colour set amongst multiple Embedded Views and the Colour Set dropdown list allows you to pick an existing colour set that you have created previously for another Embedded View.

To create a new colour set use the **Add** button which will display the **New Colours** dialog. Enter a name for the new colour set, which must be unique across the design and by default, will initialise to the same name as the Embedded View. Click OK to confirm the new colour set name and close the dialog. Once a colour set name has been chosen you are able to click the **Edit** button to make display changes specific to the selected Embedded Views.

The Embedded View display changes are performed through the same colours dialog as used for the design display settings, although when editing Embedded View settings it will additionally display the colour set name in the title bar within square brackets, e.g. Colours -[colour set name] - Layers. The colours and the **Displayed** and **True Width** values are all applicable to the Embedded View while the ones for Selectable are not. The layers to be displayed in the Embedded View are determined by the **Displayed** setting for each of the layers. Similarly, other items listed in the Colours dialog can be shown or not shown in the Embedded View by modifying their **Displayed** setting. Once the desired display characteristics have been set click the **OK** button to return to the Embedded View **Properties**.

The Lavers Only option should be checked when you want the Embedded View to display a different set of layers to the design but use the same colours (and true widths settings). The layer display details are still set up using the colours dialog for the Embedded View, but all the other dialog settings are ignored.

Note: Using Layers Only will maximise drawing efficiency and also ensures any subsequent colour changes to the design are also reflected in the Embedded View.

To reset an Embedded View back to using the same layer and colour settings as the design simply uncheck the Use Own Layers/Colours option. Note that if the last Embedded View user of a named colour set is switched back to using design layers and colours the colour set will be discarded. An Embedded View colour set may be saved and loaded in the same way as design colours.

#### Use as Magnifier

This option is similar to **Dynamic Refresh** described above, but additionally combines the Embedded View and its View Region into one creating a magnifying glass type of dynamic operation. As the Embedded View is moved over the design it displays the items underneath

through a view which can be magnified, mirrored or filtered according to the other settings of the Embedded View.

#### Interactively Modifying an Embedded View or it view region

Once added, a Embedded View can be moved, resized and flipped like any other shape item. It's shape however can not be edited except for switching between circular and rectangular.

It may also have its layer, styles, appearance or behaviour altered. To do this, double-click on the Embedded View or select it and right click to display the popup menu. Select the appropriate change menu option or select **Properties** to display all the properties of the Embedded View for editing. These includes its own set of layers and colours to display within its view.

The Show Viewed Region option, which is similar in effect to the Show in Design option that appears on the Insert Embedded View dialog, is also available from the right click popup menu. If displayed, the Embedded View Region will be shown highlighted whenever the Embedded View itself is selected. Once the Embedded View Region is displayed, it may be selected and manipulated to change the viewed region.

If **Name** or **Description** of the Embedded View is displayed it will behave and may be manipulated in the same way as any other visible attribute in the design. If the Embedded View is moved, the attribute will move with it. If the attribute is selected on its own it can be repositioned independent of the Embedded View.

The Colours dialog and Doc Shapes allows all Embedded Views to be hidden or set visible as well as defining the colour to be used for drawing their outline.

#### Selecting Multiple Embedded Views

If multiple Embedded Views are selected, the Properties dialog can be used to change their setting simultaneously.

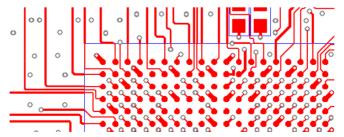

## Spacings/Styles By Area

You can now define **Spacing Rules** and **Styles** by **Area** in your **Technology**. These can be applied to design areas, layers and areas within Footprints (Components).

#### Overview

Each design has a set of styles and spacings in their **Technology** section giving the **Spacings** and Track/Via Styles to be used for different net classes in the design. You can now also set up a different set of spacings and track styles to be used by these net classes within specific

areas of the board. These are useful for defining areas around BGA components for example, where tracks and vias can be smaller and closer together in order to route out from the BGA pads. It is also useful for dividing the board into functional areas where different spacings and track/via sizes are required for some net classes.

#### Using Area Based Spacings/Styles

Use the following steps to set up your design for area based spacings and default track styles:

- Add an area and mark it as "Override within area"

- Add Class to Class Spacing By Area Name.

- Add Default rule styles by area name.

#### Adding the Area

Add an area to the board on the layer where the different spacings and styles are required. This area can be in a footprint or in the PCB design or Profile. Name the area to make it easier to refer to when later defining the spacings and styles for it.

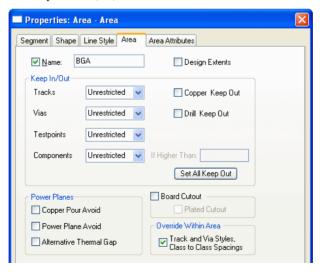

Use the **Properties** dialog to edit the area and check the **Override Within Area** box. This enables this area to be used when using a default track style for a new track, or by **Design Rule Check** when checking spacings. Ensure the area is not marked as a Keep Out area.

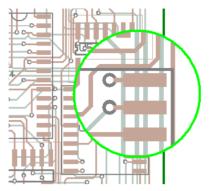

To accommodate this, areas in Footprints can now be named. If the area is in a footprint, its name will be kept when the component is added to a design. For example, if you set an area around a Ball Grid Array footprint and name it "BGA", all components using this footprint in the design will have an area called "BGA". This makes it easier when setting up spacings and styles for the area by name. The design now contains duplicate area names, but they are made unique when used in the Find Bar by adding the component name to the end of the area name, for example "BGA(U2)".

#### Setting Spacings for the Area

This is done by using the **Spacing Rules** dialog in the **Technology** to set up **Net Class** to **Net** Class Spacings for the area.

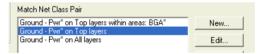

In this dialog, set the Rule Level to Match Net Class Rule and use the New button to define the area based rule. You will be presented with the Class To Class Rule dialog to setup the conditions for the spacing set to be used. Add the names of the net classes between which the spacings will apply, using wildcards to specify groups of net classes.

Now add your area name as a condition, again using wildcard characters to specify the group of areas the spacing set is to used for. For example, use "BGA\*" to define the spacings for all BGA areas.

Lastly, make sure the area specific Class to Class rules are above the more generic rules in the list, so they are matched first, otherwise they will not be used.

You will now find that the options for Design Rule Check, Online DRC, Measure Tool and most of the interactive operations will use these spacings when checking two items that are within the named areas.

Area based Class to Class spacings can also be used to define a set of spacings for a single specific inner layer of the board. You can already set the **On Layers** box to specify that a rule set applies to just the Top, Bottom or All Inner layers of the board. This functionality can be enhanced by adding a named area around the entire board on a specific inner layer and including the layer name in the Class to Class spacing rule.

## Setting the Default Routing Styles for the Area

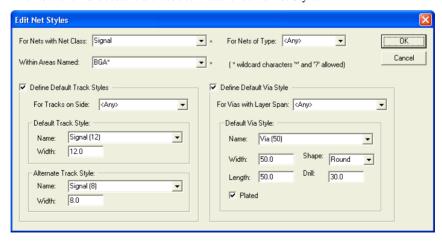

This is done by changing the way default routing styles are associated with **Net Classes**. Normally you would define the default track and via styles directly on a Net Class definition within the Technology, but if you want more flexibility over how the default styles are applied to Net Classes, you can use the Net Styles method.

If you are not already using **Net Styles**, you must enable it. To do this, use the **Design** Settings dialog and General page. Check the box within the Net Styles section. The initial set of Net Styles definitions will be created to match the default Track Styles defined on your Net Classes. They can then be edited to use wildcard net name definitions to reduce duplicates. They can also be copied to add the area name as an extra condition.

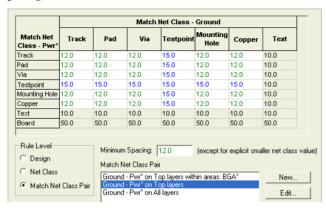

With this check box checked, there will be a new page in the **Technology** dialog for defining the **Net Styles**. Use this to build up an ordered list of default track and via styles with conditions based on Net Class names, Area names, Track Side and Via Layer Spans.

This enables you to define different default track and via styles to be used within specific areas. It also enables you to do more than just define styles by area. See the Net Styles section below for details.

In the net Styles dialog use the **New** button to define the area based styles entry. You will be presented with the Edit Net Styles dialog to setup the default styles and the conditions for them to be used. Add the name of the Net Class for which the default styles will apply, using wildcards to specify groups of Net Classes.

Now add your area name as a condition, again using wildcard characters to specify the group of areas the default styles are to be used for. For example, use "BGA\*" to define the default routing styles for all BGA areas.

Lastly, make sure the area specific Net Style definitions are positioned above the more generic ones in the list. Doing this enables them to be matched first, otherwise they will not be used.

You will now find that the interactive operations that add tracks or vias will use these default styles when the items are within the named areas. For example, changing layer or layer span will change the track style as long as the default was being used.

Area based Net Styles can also be used to define default routing styles for a single specific inner layer of the board. You can set the For Tracks on Side box to specify default track styles for the Top, Bottom or All Inner layers of the board. This functionality can be enhanced by adding a named area around the entire board on a specific inner layer, and by including the layer name in the net styles entry.

## **Net Styles**

The ability to change the definition of default track and via styles separately from **Net Classes** when routing PCB designs has been added to Pulsonix. This is done using the new **Net Styles** dialog.

This is an alternative method to taking the styles directly from the net classes. This enables you to achieve the following:

- Use wildcard characters in the net class name to reduce the number of duplicate default style definitions.

- Define different default track styles for the bottom of the board, and for inner layers.

- Define different default via styles to be used for each layer span.

- Define different default track and via styles to be used within specific areas (see previous section).

In the PCB Design under **Design Settings** and **General** page, there is a new option, **Define** default Track and via styles separately to Net Classes.

When the **Define default Track and via styles separately to Net Classes** check box is enabled under Net Styles, the initial default styles are copied from the Net Classes (already defined in the design). It will copy both used and unused Track/Via styles from the Net Class page.

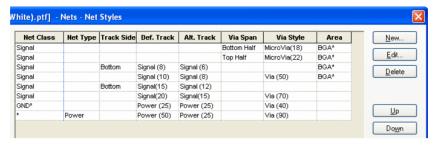

When enabled, there will be a new **Net Styles** page in the **Technology** dialog for defining the Net Styles.

Use this page to build up an ordered list of default track and via styles with conditions based on net class name, area name track side and layer span.

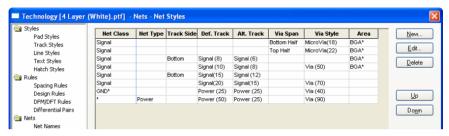

| Net Class | Net Type | Track Side | Def. Track  | Alt. Track  | Via Span    | Via Style    | Area     |

|-----------|----------|------------|-------------|-------------|-------------|--------------|----------|

| Signal    |          |            |             |             | Bottom Half | MicroVia(18) | BGA*     |

| Signal    |          |            |             |             | Top Half    | MicroVia(22) | BGA*     |

| Signal    |          | Bottom     | Signal (8)  | Signal (6)  |             |              | BGA*     |

| Signal    |          |            | Signal (10) | Signal (8)  |             | Via (50)     | BGA*     |

| Signal    |          | Bottom     | Signal(15)  | Signal (12) |             |              |          |

| Signal    |          |            | Signal(20)  | Signal(15)  |             | Via (70)     | <u> </u> |

| GND*      |          |            | Power (25)  | Power (25)  |             | Via (40)     |          |

| *         | Power    |            | Power (50)  | Power (25)  |             | Via (90)     | ···      |

The **New** and **Edit** buttons are used to create or edit a Net Style.

#### **Net Styles Order**

Use the **Up** and **Down** buttons to order the net styles entry.

When adding a new track or via to the design, the style to be used is searched for through the **Net Styles** entries defined in the design, in the order defined in this dialog. The search will continue until a match is found taking into consideration the net class name, track layer side, via layer span and an area name (if within a styles override area).

When adding a track and you are using the default track width, adding a corner will check the position for being within a Styles and Spacings override area, and the style changed if needed. This functionality is the same for vias.

You should ensure that the more specific entries are nearer the top of the table, and the general definitions using wildcard names and blank fields are at the bottom of the table.

#### Interactive Routing into and out of Areas

With area based styles defined, adding or editing an existing track that is using the default track style for its net class will check each time you add a corner to see if the style needs to be changed due to crossing an override area border. This is further enhanced when Online DRC is enabled, as the track will then stop at the edge of the styles override area, thus forcing the next corner to be added on the edge so that the style change can be on the area boundary. Click once to add a corner on the area edge and carry on the other side of the area with the different style. This allows you to easily route out of a BGA area using thin tracks running closer to each other, and then click on the area boundary to swap to using thicker tracks and a larger spacing on the other side.

The area based track style changes only happen when adding or editing a track, and not when moving track segments. If you move track segments into one of these areas and want them to take the different style defined for the area, use the Use Default Track/Via Style option described below. Conversely, if a track has been added that changed styles by crossing an area and you did not want it to, select the track and use Change Style to set it back to the required width.

#### **Differential Pair Routing**

If you have the **High Speed** option, when adding a **Differential Pair** track in paired mode. the track will not stop at area boundaries, or have their style changed when adding a corner. If you do need to achieve a style change when entering an override area, stop short of the area edge and use the Start Mirroring Paired Track option to separate the two tracks. These tracks will now stop at the area edge and change style after adding a corner on the area boundary. Join the tracks back together on the other side of the area edge to carry on adding paired tracks with the new width.

#### Forcing a Track to Use the Default Style

If you have existing areas already containing routing that you are overriding styles for, or you change the area based styles after completing some routing, you can change the existing tracks and vias to use the new default styles by using the Use Default Track/Via Style option.

Frame select the area and its contents and use the Use Default Track/Via Style option from context menu to reset the styles.

If a track goes across an area boundary it will be split so that the two halves can have different styles.

#### **Autorouting Considerations**

At this point in time, the Autorouter will not obey area based rules or styles. Routing in these areas should be completed using manual routing methods first and locked before using the Autorouter to complete the remaining nets of the design.

#### **Disconnect Track End in Select Mode**

You can now use Disconnect Track End in PCB or Disconnect Con End in the Schematic editor in select mode on the first or last segment of a track attached to an item. With the item selected, the **Disconnect Track/Con End** option is available on the context menu.

You can also now use Disconnect Track End or Disconnect Con End on a selected pad, component, or in fact on any selection that contains items attached by tracks or Schematic **connections**. This enables you to move the selected items and leave the track ends exactly where they were. If using within a Schematic design and the design is not in **Safe Mode**, the pins will be removed from their nets.

#### **Auto Weld Selection**

You can now select items and if a suitable track or pad is selected, Auto Weld Selection will be available on the context menu. This allows you to weld items without having to move them, for example after replacing a Component where the Component has dangling tracks or after using the **Gerber Import** options.

## **Footprint Wizard - Rotate Breakouts by Quadrant**

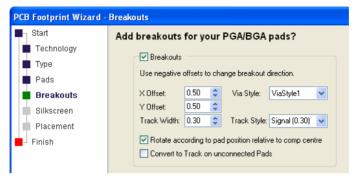

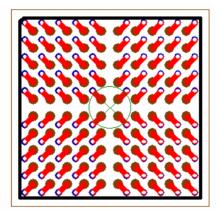

There is a new check box on **Breakouts** page of the **Footprint Wizard** for **BGA** devices, this allows the breakouts to be rotated according to the 'quadrant' in which each pad lies relative to the centre of the component.

Check the Rotate according to pad position relative to comp centre check box.

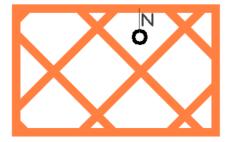

When checked, the effect will look like this:

This option is dynamic on use of the check box so using it will toggle between both methods enabling you to view the effects of this switch.

## **Track Edit Improvements**

## Track/Via Pushing

Pulsonix has an improved algorithm to produce better results when track pushing and now has two new modes. You can use Pull Tight mode to make use of 45 degree smoothing to minimise track lengths, or use Plough mode to minimise the changes to existing track paths by forcing the segment pushed to wrap around the track being added.

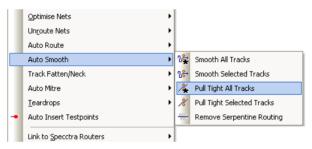

## **Pull Tight Tool**

The new **Pull Tight Tracks** tool is used to smooth an existing track pattern making use of 45 degree segments to ensure a minimum length. This command will attempt to remove corners from a track path whilst retaining the connectivity and not introducing any design rule errors. The pull tight process will introduce segments to produce a minimum length track using alternate 45 and orthogonal angle track segments.

Use from the context menu for selected Tracks,.

Or use from the **Tools** menu and **Auto Smooth**> sub menu as an alternative to **Smooth**.

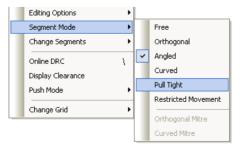

#### Pull Tight during Insert Track

The new **Pull Tight** segment mode has been added for adding track segments. This is available on the context menu under **Segment Mode>** when adding or editing tracks.

When routing in tight areas of the design, this can quickly produce results which are very space-efficient. This mode will 'wrap' tracks around obstacles and pull the result tight to

minimize the track length. In this mode you don't have to click to make a corner, the track path follows your cursor movement, even automatically removing loops as it routes.

#### Auto Finish

In addition, a new mode for auto-completion has been added. With this mode enabled, instead of the **Finish** marker, when you hit the target zone for a legal track completion, the track will automatically finish on the target pad.

To enable this mode, select the **Auto Finish** option from the **Options** dialog and **Edit Track** page. This feature is also available on the context menu under Editing Options> when editing or adding tracks.

## **Component Body and Clearance Areas**

New Area types for Component Body and Clearance Areas replace Placement Areas within an area.

A Body area defines the 'actual' shape of the physical Component body and is used for example, to determine if a testpoint is under a Component.

A Clearance area defines additional space around a Component. For example, to allow for the full opening of placement machine jaws.

Clearance areas on different Components may overlap, provided that any body areas are legal but Clearance areas and Body areas may not overlap. When using Component pushing, it is the Component Body area and Clearance area of the other Component that are used. Where

Clearance areas are not used on Components, the Body area is used for the pushing boundary and Component to Component spacing. Where a Body area has not been defined for the Component, the component bounding box (calculated by Pulsonix) will be used.

The Body area height value is used when the 3D Viewer feature is used.

Additional Component to Component spacing is applied between Body areas and not to Clearance areas.

The picture below shows how a Component can have both Body and Clearance areas defined and be different in shape. When the Clearance area of U5 comes into contact with the Body area of U4, U4 will be pushed.

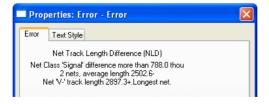

## **Net Class Track Length Difference**

You can now define the maximum track length difference between nets using the same net class. This can be done in the **Technology** under **Net Class** and **Rules** tab.

Nets using the net class with this rule will be checked when using the DRC option, Nets and **Track Length** options selected. If an error exists, an NLD error marker will be displayed. A more verbose error message will be shown in the Properties dialog of the relevant error marker.

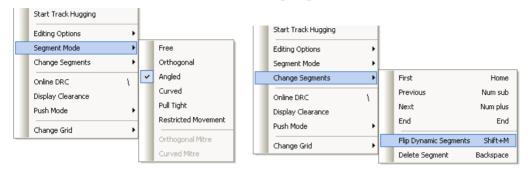

## **Segment Mode Menu Changes**

The **Segment Mode** menu items have been rationalised on the context menu. The existing three levels of nesting on the context menu has been removed

The **Segment Mode** menu has been moved up one level.

The options (Flip Dynamic Segments and Delete Segments) from the Edit Segment submenu have been moved onto the Change Segments menu.

The **Restricted Movement** option has been moved onto **Segment Mode** menu as another mode.

The Orthogonal Mitre and Curved Mitre options have been moved from the Editing Options submenu and put on the Segment Mode menu.

## Thermal Rules – Alternative Spoke Rotations

Under the **Technology** and **DFM/DFT Rules** dialog, there is a new switch **Try Alternative Rotation.** When selected, this will enable Pulsonix to attempt rotating the thermal pattern by half the spoke step if the normal pattern does not produce enough connected spokes according to the **Minimum Spokes** rule you define.

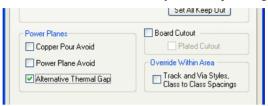

## **Alternative Thermal Gap Shape**

You can mark an **Area** as the shape to be used as the thermal relief gap for a pad which falls inside that area.

In the **Properties** dialog of the selected area, you must check the **Alternative Thermal Gap** check box. The area must reside on the layer that the plane is generated for.

When generated, the thermal spokes will follow the **DFM DFT Rules** as defined in the **Technology** and will extend to the outer edges of the area. This can be seen in the diagram below in the bottom right hand corner of the area.

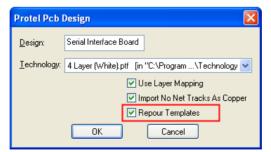

## **Re-pouring Protel Templates**

During a **Protel PCB design import**, there is now a check box which will re-pour the templates. This is available because poured copper in Protel uses single line segments and can cause slow the import process considerably.

#### Templates – Set Pour Order

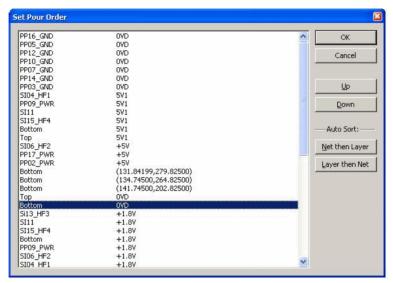

You can now view and set the Poured Templates order of all the templates in your design using the **Pour Templates Order** dialog on the **Utilities** menu. This dialog allows you to see and sort them into the order in which they should be poured.

The **Set Pour Order** dialog is used to determine the order in which templates are poured when you use the **Pour All** command. Using the dialog is an alternative to the **Ordered Template Pour** interactive method or the setting of pour order for individual Templates using Properties.

The dialog shows the templates in your design, excluding templates on powerplane layers which are not considered for Pouring.

Each entry in the list shows the layer on which the template appears, and the net (if any) to which it is assigned. Where a template has no net, the position of one corner of the template shape will be shown.

You can use the **Up** and **Down** buttons at the right-hand side of the dialog to move a particular template up or down the order, by selecting the required template in the list and clicking the button.

#### **Auto Sort**

To help you quickly arrange your templates into a reasonable order, two buttons are provided which will sort the templates based on their net and their layer. You can choose to sort either by net first then layer, or layer first then net. This should be sufficient to give you a good starting point for making any specific ordering choices. In the 'nested' templates example shown above, you could sort the templates by layer then net, then check that the net of the inner template appears before the net of the outer one.

## **Negative Text on Power Planes**

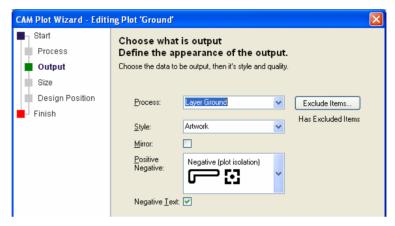

From within the **CAM Plot Wizard**, you can now specify how text on a power plane will be plotted when plotting it in Negative mode.

By checking the **Negative Text** check box, on power planes it gives you text which is cut out of the plane, this allows a negative plot to contain text without having to combine with a positive. The text has no 'box' around it, leaving it unchecked will produce text inside the 'box'.

Below are examples showing both methods of plotting text, as 'boxed' text and as 'engraved' text.

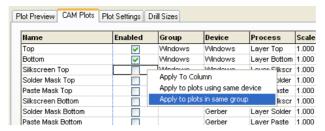

## **Plot Groups in CAM Plot**

You can now group plots using the **Plot Group** name option. This enables sets of plots of the same type to be enabled or disabled.

The **Group** column only appears if any of the plots have a group name defined.

The **Enabled** setting (box checked or unchecked) can be **applied to plots in the same group** by selecting this option from the context menu. For example, you could group plots by output device or process if you wish, i.e. Windows/Gerber etc. or Documentation/Manufacturing/Prototype etc.

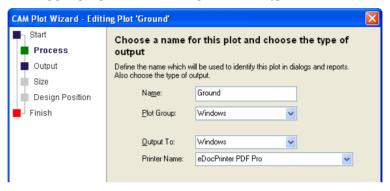

You can create a plot using the CAM Plot Wizard and add the plot to the Plot Group. Either select an existing plot group name from the drop down list or type a name in.

If you wish to add existing plots to a group, from within the CAM Plots page, you can select a name from the **Group** drop down list or type a name in.

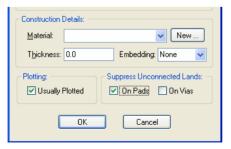

## **Suppress Unconnected Lands**

You can choose to suppress unconnected lands and/on vias or through-hole pads on an electrical layer (only vias can be suppressed on an outer layer). The land is not drawn and will not be plotted. A pad is unconnected if there is no track connected to it on that layer, and it is not contained in a Template on that layer and on the same net. The land is still used for spacing checks against items on other nets.

To enable this mode, you must create (New) or Edit the layer definition within the Technology and Layers dialog. Select the On Pads and/or On Vias check boxes under the Suppress Unconnected Lands: section.

## Case-sensitive Drill IDs

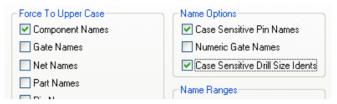

There is now a switch for **PCB Designs** in the **Design Settings** dialog, **Naming** page and **Name Options** to specify if the drill size idents can be case sensitive.

Note that case sensitive idents could already be created in the previous version (V5.1), but a Unique Drill ID warning was produced every time you entered the drill size table dialog. This no longer happens when this check box is selected.

Also, if drill idents are defined as case sensitive (using the **Case Sensitive Drill Size Idents** option), any new idents generated for new pad styles will use a lower-case letter if the style is plated.

## **Checking between Hatch Lines**

There is a new design rule option to check connectivity of items between Hatch lines. The **Check between hatch lines** option is available in the **Technology** under **Design Rules** and **Hatched Copper**.

If the Check between hatch lines option is checked, the Net Connectivity Checks in DRC and Optimise Nets functions will check that there is no break in connectivity as a result of items falling between hatch lines. This additional checking has a performance penalty, but should be used if you are using hatched copper with a large separation between lines. When this option is not checked, hatched copper is considered to be a solid shape and any item within its perimeter is connected.

With this check box selected, the error reported is Net Split/Incomplete (N) when the item falls inside the Hatch area and is on the same net but not connected.

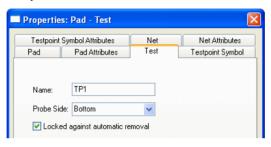

## Delete Testpoints - Locked Against Automatic Removal

This feature was added in V5.1 and released in one of the later patches during Q1 of 2009 but was not previously documented.

In the Auto Insert Testpoints option on the Tools menu, you can now delete testpoints which are not locked against automatic delete.

Selected Testpoints can be locked from within the **Properties** dialog using the **Test** page. The check box Locked against automatic removal should be used. By default, new Testpoints added already have this check box selected.

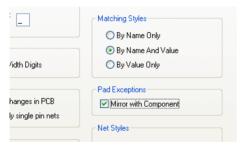

#### Mirror Pad Stack

The option in the section was created in V5.1 and released in one of the later patches during O1 of 2009 but was not previously documented.

You can use the Mirror with Component check box in the Design Settings option and **General** page, **Pad Exceptions** to achieve mirrored pad stacks.

When checked, any pad style layer exceptions used on pads in mirrored Components will have their layer swapped to the other side. This was added specifically for Through-hole pad stacks where Top side or Bottom side pad stacks were defined. Surface Mounted pad stacks are left unaffected.

## **Library Changes**

In Pulsonix 6.0, new Parts libraries have been added and some existing libraries modified, the changes comprise the following:

- The contents of Footprints.pfl have been split across a new SM Footprints.pfl library

and the existing Footprints library. The Footprints library now includes all non-surface

mounted footprints.

- The **Avago HPCL-3150** range has been added (**Avago.pal**). These devices demonstrate the new multiple PCB pin mapping feature.

- The Texas Instruments TMS320 32-Bit (DSP) Digital Signal Controller device range has been added (TSM320.pal).

- The Fairchild Semiconductor FDC2512 N-Channel MOSFET devices have been added (Fairchild FDC2512.pal). These devices demonstrate the new multiple PCB pin mapping feature.

- The Coilcraft 1008CS (2520) series of chip inductors has been added (Coilcraft.pal).